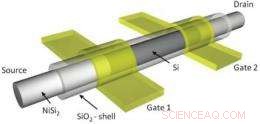

O núcleo do transistor reconfigurável consiste em uma estrutura de nanofio embutida em um invólucro de dióxido de silício. Elétrons ou buracos fluem da fonte em uma extremidade do nanofio através de duas portas para o dreno na outra extremidade do nanofio. Uma porta é usada para programar a polaridade p ou n, enquanto a outra porta ajusta a condutância através do nanofio. Crédito da imagem:© Namlab gGmbH

(PhysOrg.com) - A maioria dos dispositivos eletrônicos de hoje contém dois tipos diferentes de transistores de efeito de campo (FETs):tipo n (que usa elétrons como portadores de carga) e tipo p (que usa buracos). Geralmente, um transistor pode ser apenas um tipo ou outro, mas não ambos. Agora em um novo estudo, pesquisadores projetaram um transistor que pode se reconfigurar como tipo n ou tipo p quando programado por um sinal elétrico. Um conjunto desses "transistores universais" pode, em princípio, realizar qualquer operação lógica booleana, o que significa que os circuitos podem realizar o mesmo número de funções lógicas com menos transistores. Essa vantagem pode levar a um hardware mais compacto e novos projetos de circuito.

Os pesquisadores que projetaram o transistor, liderado por Walter M. Weber na Namlab gGmbH em Dresden, Alemanha, publicaram o novo conceito em uma edição recente da Nano Letras .

“Nanofios sintéticos são usados para realizar a prova de princípio, ”Weber disse PhysOrg.com . "Contudo, o conceito é totalmente transferível para a tecnologia de silício CMOS de última geração e pode fazer uso de processos autoalinhados ”.

O núcleo do novo transistor consiste em um único nanofio feito de uma estrutura de metal semicondutor que está embutido em uma concha de dióxido de silício. Elétrons ou buracos fluem da fonte em uma extremidade do nanofio através de duas portas para o dreno na outra extremidade do nanofio. As duas portas controlam o fluxo de elétrons ou lacunas de maneiras diferentes. Uma porta seleciona o tipo de transistor, escolhendo usar elétrons ou lacunas, enquanto a outra porta controla os elétrons ou buracos, ajustando a condutância do nanofio.

Usar uma porta para selecionar a configuração do tipo p ou n é bastante diferente dos transistores convencionais. Em transistores convencionais, A operação do tipo p ou n resulta da dopagem que ocorre durante o processo de fabricação, e não pode ser alterado uma vez que o transistor é feito. Em contraste, o transistor reconfigurável não usa nenhum doping. Em vez de, uma tensão externa aplicada a uma porta pode reconfigurar o tipo de transistor mesmo durante a operação. A voltagem faz com que a junção Schottky perto do portão bloqueie o fluxo de elétrons ou lacunas através do dispositivo. Então, se os elétrons estão bloqueados, orifícios podem fluir e o transistor é do tipo p. Aplicando uma voltagem ligeiramente diferente, a reconfiguração pode ser alternada novamente, sem interferir com o fluxo.

Os cientistas explicam que a chave para fazer essa reconfiguração funcionar é a capacidade de ajustar o transporte eletrônico em cada uma das duas junções (uma por portão) separadamente. Suas simulações mostraram que a corrente é dominada por túneis, sugerindo que a geometria do nanofio desempenha um papel importante na capacidade de controle de junção independente.

Como o transistor reconfigurável pode realizar as funções lógicas de FETs do tipo p e n, um único transistor pode substituir um FET do tipo p e n em um circuito, o que reduziria significativamente o tamanho do circuito sem reduzir a funcionalidade. Mesmo nesta fase inicial, o transistor reconfigurável mostra características elétricas muito boas, incluindo uma relação liga / desliga de registro e corrente de fuga reduzida em comparação com FETs de nanofios convencionais. No futuro, os pesquisadores planejam melhorar ainda mais o desempenho do transistor.

“Estamos variando as combinações de materiais para aumentar ainda mais o desempenho do dispositivo, ”Weber disse. "Mais para frente, primeiros circuitos que implementam esses dispositivos estão sendo construídos. ... O maior desafio será incorporar os sinais de gate extras no layout da célula, permitindo uma interconexão flexível com os outros transistores. ”

Copyright 2011 PhysOrg.com.

Todos os direitos reservados. Este material não pode ser publicado, transmissão, reescrito ou redistribuído no todo ou em parte sem a permissão expressa por escrito da PhysOrg.com.