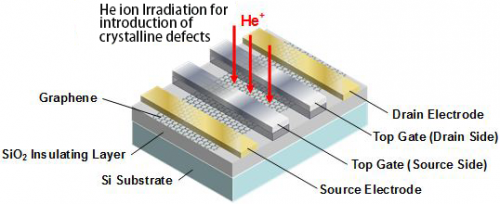

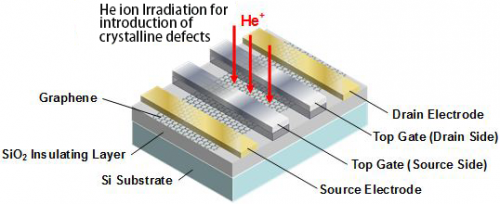

p Ilustração esquemática de um protótipo de transistor de grafeno.

p Ilustração esquemática de um protótipo de transistor de grafeno.

p Os pesquisadores da AIST desenvolveram um transistor de grafeno com um novo princípio operacional. No transistor desenvolvido, dois eletrodos e duas portas superiores são colocados no grafeno e o grafeno entre as portas superiores é irradiado com um feixe de íons de hélio para introduzir defeitos cristalinos. Os enviesamentos de portão são aplicados aos dois portões superiores de forma independente, permitindo que as densidades de portadores nas regiões de grafeno com barreira superior sejam efetivamente controladas. Uma relação liga / desliga da corrente elétrica de aproximadamente quatro ordens de magnitude foi demonstrada a 200 K (aproximadamente -73 ° C). Além disso, a polaridade do transistor pode ser controlada eletricamente e invertida, que até agora não foi possível para transistores. Esta tecnologia pode ser utilizada na tecnologia de produção convencional de circuitos integrados à base de silício, e espera-se que contribua para a realização de eletrônicos de consumo ultrabaixo, reduzindo a tensão de operação no futuro. p Os detalhes desta tecnologia foram apresentados na Reunião Internacional de Dispositivos Eletrônicos de 2012 (IEDM 2012) realizada em São Francisco, EUA., de 10 a 12 de dezembro, 2012

p Nos últimos anos, o aumento do consumo de energia associado à disseminação dos terminais móveis de informação e o progresso nos dispositivos de TI tem se tornado uma preocupação. A demanda da sociedade por redução da energia consumida por dispositivos eletrônicos de informação está aumentando. Embora as tentativas de reduzir a energia consumida por circuitos integrados de grande escala (LSIs) tenham sido avançadas, a estrutura do transistor convencional é considerada como tendo limites inerentes. Enquanto isso, mobilidade de elétrons do grafeno, que representa a facilidade do movimento do elétron, é pelo menos 100 vezes maior do que o silício. Também se espera que o grafeno possa ser usado para resolver os problemas dos limites inerentes ao silício e outros materiais. Portanto, o grafeno tem o potencial de remover o obstáculo para reduzir a energia consumida pelos LSIs, e espera-se que o grafeno seja usado como um material para transistores de ultra-baixo consumo de energia da era pós-silício que utilizam novos filmes atômicos funcionais.

p Figura 1:Princípios de operação do novo transistor de grafeno e transistores convencionais.

p Figura 1:Princípios de operação do novo transistor de grafeno e transistores convencionais.

p Contudo, quando o grafeno é usado em um transistor de comutação, a corrente elétrica não pode ser suficientemente interrompida, porque o grafeno não tem gap. Também, embora haja tecnologia para formar lacunas de banda, a mobilidade do elétron diminui quando o gap necessário para a comutação é formado. Portanto, é necessário um transistor de grafeno com um novo princípio de operação que pode realizar a operação de chaveamento efetivamente com um pequeno gap.

p O princípio de operação do transistor de grafeno recentemente desenvolvido é mostrado nas Figs 1 (a) a 1 (c). A fim de criar uma lacuna de transporte em grafeno do canal entre os dois portões superiores, um microscópio de íon hélio foi usado para irradiar íons de hélio a uma densidade de 6,9 x 10

15

íons / cm

2

para introduzir defeitos cristalinos. A banda de energia do grafeno em ambos os lados do canal pode ser modulada por controle eletrostático aplicando polarizações às portas superiores. A polaridade das portadoras no grafeno pode ser alterada entre o tipo n e o tipo p, dependendo da polaridade das polarizações aplicadas às portas superiores. Quando as polaridades em ambos os lados do canal diferem, o transistor está desligado (Fig. 1 (b)). Quando as polaridades são iguais, o transistor está ligado (Fig. 1 (c)). Quando um transistor convencional (Figs. 1 (d) a 1 (f)) está em um estado desligado, o transporte do transportador é bloqueado por uma barreira formada na extremidade do lado da fonte ou do dreno do canal que tem a lacuna de transporte. Contudo, como mostrado na Fig. 1 (e), a corrente de fuga do transistor no estado desligado é grande, porque apenas uma pequena barreira é formada. Enquanto isso, como mostra a Fig. 1 (b), a lacuna de transporte no transistor desenvolvido funciona como uma barreira maior do que a dos transistores convencionais (Fig. 1 (e)) e bloqueia a transferência de carga. Como resultado, é possível obter um estado desligado superior ao dos transistores convencionais.

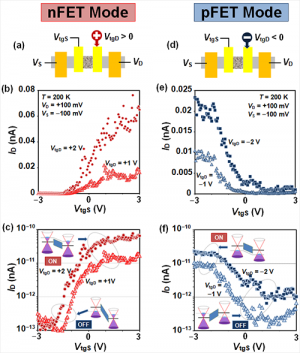

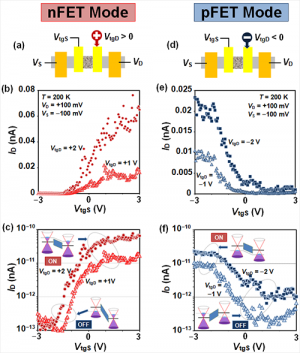

p Figura 3:Relação liga / desliga da corrente elétrica do novo transistor de grafeno.

p Figura 3:Relação liga / desliga da corrente elétrica do novo transistor de grafeno.

p No transistor desenvolvido, o comprimento do canal, em que a mobilidade geralmente se deteriora, pode ser reduzido a um comprimento menor do que o dos transistores convencionais. Além disso, porque o transistor desenvolvido pode atingir um estado desligado eficiente com uma pequena lacuna de transporte, a lacuna de transporte pode ser menor do que a dos dispositivos convencionais. Devido a essas propriedades, a operação liga / desliga do transistor pode ser realizada mais rapidamente do que com transistores convencionais, e, portanto, acredita-se que um LSI com menor consumo de energia pode ser realizado reduzindo a tensão de operação do circuito. Além disso, os transistores podem ser produzidos usando a tecnologia de fabricação convencional para circuitos integrados de silício, como litografia, deposição, e processos de dopagem, e também pode ser facilmente produzido em escala de wafer.

p A fim de demonstrar a operação do transistor do novo princípio de operação, um transistor foi fabricado formando eletrodos de fonte e dreno e um par de portas superiores em um grafeno de camada única isolado de grafite. Uma dose apropriada de íons de hélio foi aplicada entre as portas superiores para fazer um canal irradiado de íons de hélio (Fig. 2, linha pontilhada azul), e o grafeno desnecessário externo foi irradiado com uma grande dose de íons de hélio para torná-lo um isolante (Fig. 2, linha pontilhada vermelha). Como resultado, o canal do transistor tem 20 nm de comprimento e 30 nm de largura.

p Figura 4:Demonstração da operação do transistor em que a polaridade do transistor foi eletricamente invertida. VtgD é a tensão da porta do lado do dreno.

p Figura 4:Demonstração da operação do transistor em que a polaridade do transistor foi eletricamente invertida. VtgD é a tensão da porta do lado do dreno.

p A operação liga / desliga do transistor fabricado foi realizada na baixa temperatura de 200 K (aproximadamente −73 ° C). Os terminais de fonte e dreno foram aplicados com vieses de −100 mV e +100 mV, respectivamente. A polarização da porta do lado do dreno foi fixada em -2 V, and that of the source-side gate was swept from −4 V to +4 V and the electric current flowing between the source and drain electrodes was measured. An on/off ratio of approximately four orders of magnitude was observed (Fig. 3).

p In the developed transistor, the on state or off state is controlled according to whether the polarities of the voltages applied to the two top gates are the same or different. Therefore, by fixing one gate bias and changing its polarity, it is possible to control whether the transistor operation by sweeping the other gate voltage is n-type or p-type. In the present experiment, voltages of −100 mV and +100 mV were applied to the source and drain terminals, respectivamente. The relation between the source-drain current and the bias of the source-side gate when the gate voltage of the drain-side, V

tgD , is fixed to be positive (Fig. 4(a)), is shown in Fig. 4(b). A logarithmic plot of the same data is shown in Fig. 4 (c). Aqui, when the gate voltage of the source-side is negative, the transistor is off, and when it is positive, the transistor is on. So it operates as an n-type transistor. Enquanto isso, the relation between the source-drain current and the bias of the source-side gate when the gate voltage of the drain-side is negative (Fig. 4(d)), is shown in Figs 4(e) and 4(f). Nesse caso, when the gate voltage of the source-side is negative, the transistor is on, and when positive, the transistor is off. So it operates as a p-type transistor. Em outras palavras, it was actually demonstrated that the polarity of a single transistor can be inverted by electrostatic control.

p The transistor polarity of conventional silicon transistors is determined by the type of ion for doping, so it is not possible to change the polarity once a circuit is formed. Contudo, because the polarity of the developed transistor can be electrostatically controlled, it is possible to realize an integrated circuit whose circuit structure can be electrically changed.

p The researchers are aiming to realize CMOS operation in which transistor polarities can be changed through electrical control. They are also aiming to create a device prototype using a large-scale wafer with graphene synthesized by the CVD method (chemical vapor-phase deposition method). Ao mesmo tempo, efforts to achieve higher-quality graphene will be made in order to improve the on/off ratio of electric current at room temperature and carrier mobility.