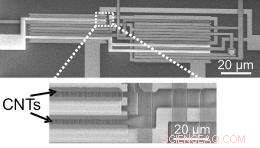

p Uma imagem de microscópio eletrônico mostrando transistores de nanotubos de carbono (CNTs) dispostos em um circuito lógico integrado.

p Uma imagem de microscópio eletrônico mostrando transistores de nanotubos de carbono (CNTs) dispostos em um circuito lógico integrado.

p (PhysOrg.com) - Os engenheiros de Stanford construíram o que acreditam ser um chip com os mais avançados elementos de computação e armazenamento feitos de nanotubos de carbono até hoje, criando uma maneira de erradicar a complicação teimosa dos nanotubos que causam curtos-circuitos. p Nanotubos, que se assemelham a canudos microscópicos de tela de arame enrolada, são amplamente vistos como a próxima geração potencial de materiais para permitir maior velocidade e eficiência energética de chips de computador.

p Os pesquisadores apresentaram seus resultados hoje no International Electron Devices Meeting (IEDM) em Baltimore, junto com outro avanço no uso de nanotubos para fazer multicamadas, circuitos tridimensionais.

p "Este corpo de trabalho ilustra que a tecnologia de transistores de nanotubos de carbono foi além do reino da descoberta científica e para a pesquisa de engenharia, "disse H.-S. Philip Wong, professor de engenharia elétrica em Stanford e co-autor do artigo. "Agora somos capazes de construir dispositivos e circuitos em uma escala de wafer, ao contrário das demonstrações anteriores do tipo 'one-of-a-kind'. Os dispositivos estão em um ambiente de circuito que é relevante para as necessidades do sistema de hoje e de amanhã."

p O punhado de transistores de nanotubos nos circuitos que a equipe fabricou não pode ser comparado às centenas de milhões de transistores em um microprocessador comercial ou chip de memória, mas o arranjo deles, a maneira como foram feitos e suas propriedades estão muito mais próximas do nível comercial do que quaisquer dispositivos de nanotubos feitos antes, disse Subhasish Mitra, professor assistente de ciência da computação e engenharia elétrica em Stanford.

p Os transistores são agrupados nas mesmas sequências "em cascata" necessárias para produzir lógica computacional e memória, e o processo usado para fazê-los é compatível com o padrão de fabricação industrial VLSI (very large scale integration).

p "Estamos muito satisfeitos com o rápido progresso feito pelos professores Wong e Mitra e suas equipes de pesquisa no desenvolvimento dessas tecnologias para ajudar a superar as barreiras para uma maior integração de complexos circuitos eletrônicos baseados em carbono, o que levará a produtos mais úteis para as gerações futuras, "disse Betsy Weitzman, vice-presidente executivo e diretor do Programa Focus Center de Pesquisa da Semiconductor Research Corporation, que ajudou a financiar a pesquisa, junto com a National Science Foundation.

p Os chips empregam três técnicas avançadas inventadas em Stanford para superar problemas endêmicos associados aos nanotubos. 1, inventado em 2007, permite que os transistores funcionem independentemente de os nanotubos componentes ficarem perfeitamente retos. Outro, inventado em 2008, permite a fabricação em escala VLSI de transistores de nanotubos em um chip. Aquele anunciado hoje no IEDM, é um processo para a remoção confiável de nanotubos que sempre conduzem corrente elétrica, mesmo quando não deveriam. Esses problemáticos nanotubos "metálicos" podem causar curto-circuito nos transistores se eles não forem removidos. A dificuldade que os pesquisadores enfrentaram é encontrar maneiras de remover todos os nanotubos problemáticos, sem danificar qualquer outra parte de um circuito, incluindo os nanotubos que se comportam adequadamente.

p A nova técnica, que os pesquisadores chamam de remoção de nanotubo metálico compatível com VLSI (VMR), baseia-se em uma ideia proposta pela primeira vez por Paul Collins e colegas da IBM em 2001. Essa ideia era quebrar os nanotubos expondo-os a altas correntes. A equipe de Stanford agora tornou a ideia prática em uma escala de VLSI, criando uma grade de eletrodos que eliminam os nanotubos indesejados. Essa mesma grade de eletrodo pode então ser gravada para produzir qualquer projeto de circuito, incluindo aqueles que fazem uso das técnicas desenvolvidas por Stanford mencionadas acima.

p O autor principal do artigo VMR apresentado no IEDM é o estudante de graduação em engenharia elétrica de Stanford, Nishant Patil. Outros autores incluem estudantes de graduação em engenharia elétrica Albert Lin, Jie Zhang e Hai Wei, e o estudante de graduação Kyle Anderson.

p

Circuitos de nanotubos 3-D

p Cinco membros da equipe (Wei, Patil, Lin, Wong e Mitra) imediatamente seguiram o artigo VMR no IEDM com outra apresentação descrevendo o primeiro circuito integrado tridimensional de nanotubo de carbono de multicamadas.

p Como garagens de estacionamento multinível, circuitos tridimensionais permitem o acondicionamento de mais unidades - neste caso, transistores - em uma área confinada. Em chips, a terceira dimensão também pode reduzir o comprimento de alguns fios de interconexão, reduzindo a energia necessária para a transmissão de dados. Embora os engenheiros tenham recentemente começado a fazer progressos na construção de circuitos tridimensionais, empilhando e conectando camadas feitas com materiais convencionais, o trabalho de Stanford mostra que isso pode ser feito com nanotubos de uma forma que é integrada desde o início como um design 3-D, produzindo uma maior densidade de conexões entre as camadas.

p Indicando que o progresso pode ser possível com nanotubos, os pesquisadores de Stanford conseguiram criar um protótipo de chip de três camadas com dezenas de transistores de nanotubos que foram conectados em portas lógicas funcionais por nanotubos e fiação de metal. O que tornou a façanha possível, Mitra disse, foi o uso de um processo de temperatura relativamente baixa que os pesquisadores desenvolveram no ano passado, no qual nanotubos são transferidos de um wafer de quartzo para um chip de silício.

p Um desafio restante é aumentar o número de nanotubos que podem ser devidamente padronizados em uma determinada área de um chip, para permitir a fabricação dos milhões de transistores que os projetos modernos exigem. Esse não é um obstáculo que os pesquisadores esperam deixar sem ser explorado.

p Ambos os projetos foram apoiados pelo Focus Center Research Program e pela National Science Foundation's Directorate for Computer and Information Science and Engineering (CISE).

p "NSF e em particular CISE, está muito interessada em explorar novos caminhos interessantes para obter melhorias contínuas de desempenho de hardware além dos limites da Lei de Moore, "disse Sampath Kannan, um diretor de divisão do CISE na National Science Foundation.

p "A equipe liderada pelos professores Mitra e Wong, apoiado por vários subsídios do CISE, é pioneira na pesquisa ao longo de uma dessas avenidas. Seus novos resultados na técnica em escala VLSI para lidar com nanotubos de carbono metálico para projeto de circuitos e sua demonstração experimental de circuitos CNT compatíveis com VLSI imunes a imperfeições nos aproximam de tornar os circuitos integrados usando nanotubos de carbono uma realidade prática. "

p Fornecido pela Stanford University (notícias:web)