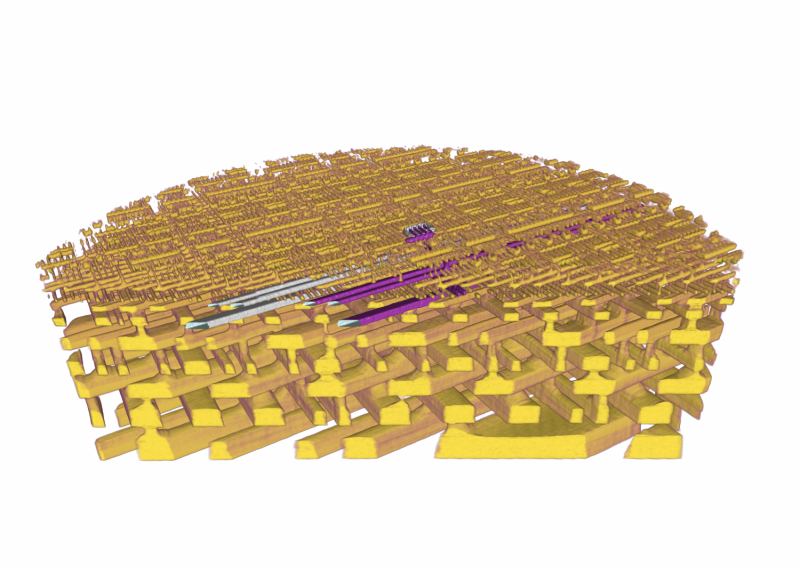

Representação 3D da estrutura interna de um microchip (um processador Intel). A visualização mostrada está exatamente no nível em que os transistores estão. O material em amarelo é cobre - mostrando as conexões do circuito do processador que ligam os transistores individuais entre si. Ilustrar, várias interconexões cujas linhas podiam ser seguidas através do volume examinado foram coloridas. As linhas mostradas individualmente têm cerca de 45 nanômetros de largura (45 milionésimos de milímetro); Em tudo, foi examinada uma peça do processador com cerca de 10 micrômetros (10 milésimos de milímetro) de diâmetro. Crédito:Instituto Paul Scherrer / Mirko Holler

Pesquisadores do Instituto Paul Scherrer PSI fizeram imagens 3D detalhadas de um chip de computador disponível comercialmente. Isso marca a primeira vez que um método não destrutivo visualizou os caminhos da fiação interna de um chip (apenas 45 nanômetros - 45 milionésimos de milímetro - de largura) e seus transistores de 34 nanômetros de altura claramente sem distorções ou deformações. É um grande desafio para os fabricantes determinar se, no fim, a estrutura de seus chips está de acordo com as especificações. Portanto, esses resultados representam uma aplicação importante de um método de tomografia de raios-X que os pesquisadores do PSI vêm desenvolvendo há vários anos. Em seu experimento, os pesquisadores examinaram um pequeno pedaço que haviam cortado do chip com antecedência. Esta amostra permaneceu intacta durante a medição. O objetivo agora é estender o método de forma que ele possa ser usado para examinar chips completos. Os pesquisadores conduziram os experimentos no Swiss Light Source SLS do Paul Scherrer Institute.

Eles relatam seus resultados na última edição da revista. Natureza .

A fiação elétrica em muitos dos chips eletrônicos em nossos computadores e telefones celulares tem apenas 45 nanômetros de largura, os transistores de 34 nanômetros de altura. Embora seja uma prática padrão hoje produzir estruturas tão delicadas, continua sendo um desafio medir a estrutura exata de um chip acabado em detalhes para verificar, por exemplo, se for construído de acordo com as especificações. Hoje em dia, para tais exames, os fabricantes usam principalmente um método em que camada após camada do chip é removida e, em seguida, após cada etapa, a superfície é examinada com um microscópio eletrônico; isso é conhecido como FIB / SEM - feixe de íons focado / imagem de microscópio eletrônico de varredura.

Agora, pesquisadores do Instituto Paul Scherrer PSI usaram raios-X para obter imagens 3-D não destrutivas de um chip, de modo que os caminhos das linhas condutoras e as posições dos transistores individuais e outros elementos do circuito se tornassem claramente visíveis. A resolução da imagem que conseguimos produzir é comparável ao método de exame FIB / SEM convencional, explica Mirko Holler, líder do projeto. Mas fomos capazes de evitar duas desvantagens significativas:em primeiro lugar, a amostra permaneceu intacta, e temos informações completas sobre a estrutura tridimensional. Em segundo lugar, evitamos distorções das imagens que surgem no FIB / SEM se a superfície da fatia individual não for exatamente plana.

Posicionado com precisão nanométrica

Para seu estudo, os pesquisadores usaram um método tomográfico especial (pticotomografia) que desenvolveram e aprimoraram ao longo dos últimos anos, e que hoje oferece a melhor resolução mundial de 15 nanômetros (15 milionésimos de milímetro) para o exame de um volume comparativamente grande. No experimento, o objeto a ser estudado é radiografado em locais precisamente determinados com luz da Swiss Light Source SLS do Paul Scherrer Institute - para cada ponto iluminado, um detector mede o padrão de luz de raios-X após sua passagem pela amostra . A amostra é então girada em pequenas etapas e, em seguida, radiografada novamente em etapas após cada volta. De todo o conjunto de dados obtidos, a estrutura tridimensional da amostra pode ser determinada. Com essas medidas, a posição da amostra deve ser conhecida com uma precisão de apenas alguns nanômetros - esse foi um dos desafios particulares na criação de nossa estação experimental, Holler diz.

Em seu experimento, os pesquisadores examinaram pequenos pedaços de dois chips - um chip detector desenvolvido no PSI e um chip de computador disponível comercialmente. Cada peça tinha cerca de 10 micrômetros (ou seja, 10 milésimos de milímetro) de tamanho. Embora o exame de um chip inteiro com a configuração de medição atual não seja possível, as vantagens do método são aplicadas mesmo nesta forma, de modo que os primeiros possíveis usuários já manifestaram interesse em realizar medições no PSI.

Os pesquisadores do PSI Mirko Holler (à direita) e Manuel Guizar-Sicairos na linha de luz cSAXS da Swiss Light Source SLS do Instituto Paul Scherrer. Aqui, eles tornaram a estrutura tridimensional de um microchip visível. Crédito:Instituto Paul Scherrer / Markus Fischer

O objetivo:examinar microchips inteiros

Atualmente, estamos começando a estender o método de forma que possa ser usado para examinar microchips inteiros dentro de um tempo de medição aceitável. Então também será possível estudar a mesma área de um chip várias vezes, por exemplo, para observar como ele muda sob influências externas, explica Gabriel Aeppli, chefe da Divisão de Radiação Síncrotron e Nanotecnologia do PSI.

Uma segunda representação 3D da estrutura interna de um microchip (um processador Intel). Crédito:Instituto Paul Scherrer / Mirko Holler