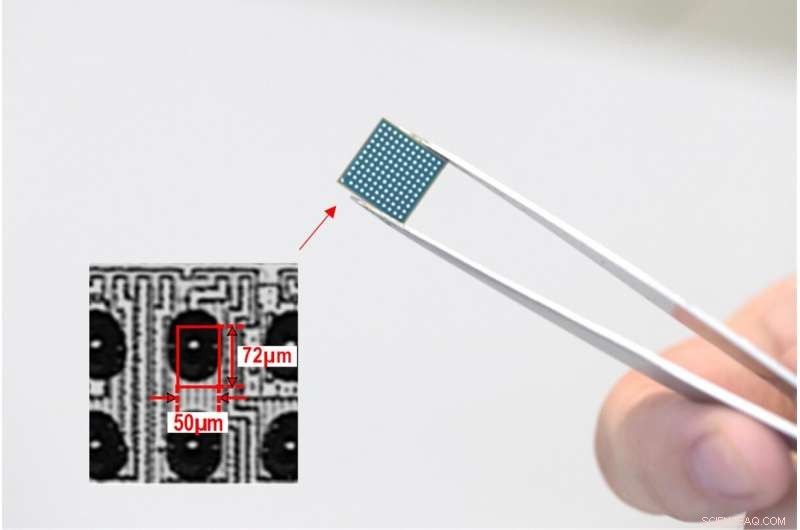

Todo o PLL totalmente digital se encaixa em uma região de 50 × 72 μm2, tornando-o o menor PLL até o momento. Crédito:Kenichi Okada

Cientistas do Instituto de Tecnologia de Tóquio (Tokyo Tech) e da Socionext Inc. projetaram o menor loop totalmente digital de fase bloqueada (PLL) do mundo. PLLs são circuitos de clock críticos em praticamente todas as aplicações digitais, e reduzir seu tamanho e melhorar seu desempenho é uma etapa necessária para permitir o desenvolvimento de tecnologias de próxima geração.

Tecnologias novas ou aprimoradas, como inteligência artificial, Comunicações celulares 5G, e a Internet das Coisas, são esperados para trazer mudanças revolucionárias na sociedade. Mas para que isso aconteça, dispositivos system-on-a-chip (SoC) de alto desempenho - um tipo de circuito integrado - são indispensáveis. Um bloco de construção central dos dispositivos SoC é o loop de bloqueio de fase (PLL), um circuito que sincroniza com a frequência de uma oscilação de referência e emite um sinal com a mesma frequência ou frequência superior. PLLs geram 'sinais de clock, 'cujas oscilações atuam como um metrônomo que fornece uma referência de tempo precisa para a operação harmoniosa de dispositivos digitais.

Para que dispositivos SoC de alto desempenho sejam realizados, os processos de fabricação de eletrônicos semicondutores devem se tornar mais sofisticados. Quanto menor for a área para implementar o circuito digital, melhor será o desempenho do dispositivo. Os fabricantes estão correndo para desenvolver semicondutores cada vez menores. Semicondutores de 7 nm (uma grande melhoria em relação ao seu antecessor de 10 nm) já estão em produção, e métodos para construir aqueles de 5 nm estão agora sendo examinados.

Contudo, neste esforço encontra-se um grande gargalo. PLLs existentes requerem componentes analógicos, que geralmente são volumosos e têm designs difíceis de reduzir.

Cientistas da Tokyo Tech e Socionext Inc., liderado pelo Prof Kenichi Okada, resolveram esse problema implementando um PLL fracionário N 'sintetizável', que requer apenas portas lógicas digitais, e nenhum componente analógico volumoso, tornando mais fácil a adoção em circuitos integrados miniaturizados convencionais.

Okada e a equipe usaram várias técnicas para diminuir a área necessária, consumo de energia e jitter - flutuações de tempo indesejadas ao transmitir sinais digitais - de seus PLLs sintetizáveis. Para diminuir a área, eles empregaram um oscilador de anel, um oscilador compacto que pode ser facilmente reduzido. Para suprimir o jitter, eles reduziram o ruído de fase - flutuações aleatórias em um sinal - deste oscilador de anel, usando 'bloqueio por injeção' - o processo de sincronizar um oscilador com um sinal externo cuja frequência (ou múltiplo) é próxima à do oscilador - em uma ampla faixa de frequências. O ruído de fase inferior, por sua vez, consumo de energia reduzido.

O design deste PLL sintetizável supera o de todos os outros PLLs de última geração em muitos aspectos importantes. Ele atinge o melhor desempenho de jitter com o menor consumo de energia e menor área (como pode ser visto na Figura 1). "A área central é 0,0036 mm2, e todo o PLL é implementado como um layout com uma única fonte de alimentação, "comenta Okada. Além disso, ele pode ser construído usando ferramentas de design digital padrão, permitindo sua rapidez, baixo esforço, e produção de baixo custo, tornando-o comercialmente viável.

Este PLL sintetizável pode ser facilmente integrado ao design de SoCs totalmente digitais, e é comercialmente viável, tornando-o valioso para o desenvolvimento do muito procurado semicondutor de 5 nm para aplicações de ponta, incluindo inteligência artificial, internet das coisas e muitos outros, onde alto desempenho e baixo consumo de energia seriam os requisitos críticos. Mas as contribuições desta pesquisa vão além dessas possibilidades. “Nosso trabalho demonstra o potencial dos circuitos sintetizáveis. Com a metodologia de projeto empregada aqui, outros blocos de construção de SoCs, como conversores de dados, circuitos de gerenciamento de energia, e transceptores sem fio, também poderia ser sintetizado. Isso aumentaria muito a produtividade do projeto e reduziria consideravelmente os esforços do projeto, "explica Okada. Tokyo Tech e Socionext continuarão sua colaboração neste campo para fazer avançar a miniaturização de dispositivos eletrônicos, permitindo a realização de tecnologias de nova geração.