Demonstração da célula de memória SOT-MRAM de alta velocidade compatível com a tecnologia 300 mm Si CMOS

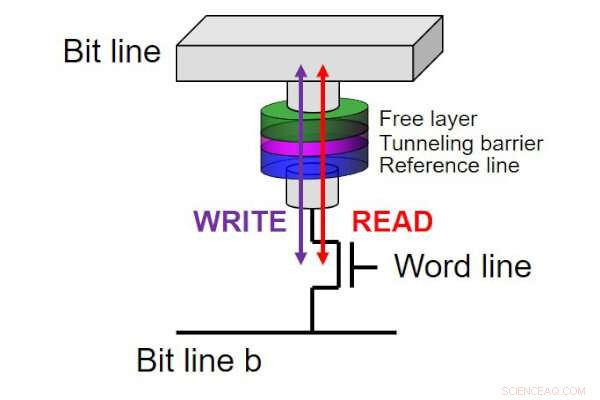

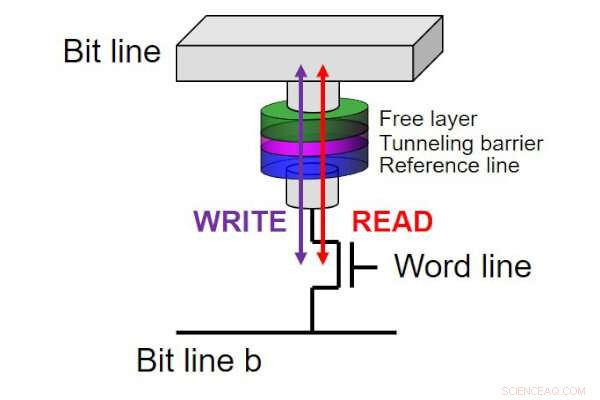

p Esquema da célula STT-MRAM (dispositivo de dois terminais). Crédito:CIES, Tohoku University

p Esquema da célula STT-MRAM (dispositivo de dois terminais). Crédito:CIES, Tohoku University

p Pesquisadores da Tohoku University anunciaram a demonstração de uma célula de memória de acesso aleatório magnetorresistiva de alta velocidade spin-orbit-torque (SOT) compatível com a tecnologia Si CMOS de 300 mm. p A demanda por circuitos integrados (ICs) de baixa potência e alto desempenho tem aumentado à medida que dispositivos de inteligência artificial (AI) e Internet das Coisas (IoT) se tornam mais amplamente adotados. Com os CIs atuais, memórias puramente baseadas em CMOS, como memória Flash embutida (eFlash) e memória de acesso aleatório estática (SRAM), são responsáveis por uma alta proporção do consumo de energia. Para reduzir o consumo de energia e ao mesmo tempo manter o alto desempenho, As memórias magnetorresistivas de acesso aleatório (MRAMs) têm sido desenvolvidas de forma intensiva. Os MRAMs de torque de transferência de rotação (STT-MRAMs) são os MRAM desenvolvidos mais intensamente. As principais empresas de semicondutores anunciaram agora que estão prontas para a produção em massa de STT-MRAM para substituição do eFlash.

p Os pesquisadores pretendem substituir SRAM por MRAM. Para substituição de SRAM, MRAM deve alcançar operação de alta velocidade acima de 500 MHz. Para atender a demanda, um MRAM alternativo, o chamado torque spin-orbit MRAM (SOT-MRAM) foi proposto, que tem várias vantagens para operação em alta velocidade. Por causa dessas vantagens, SOT-MRAM também foi desenvolvido; Contudo, a maioria dos estudos de laboratório enfoca os fundamentos dos dispositivos SOT. Para realizar a substituição de SRAM por SOT-MRAM, é necessário para demonstrar o alto desempenho da célula de memória SOT-MRAM em um substrato CMOS de 300 mm. Além disso, é necessário desenvolver o processo de integração para SOT-MRAM, por exemplo., tolerância térmica contra recozimento de 400 ° C, que é um requisito do processo back-end-of-line padrão do CMOS.

-

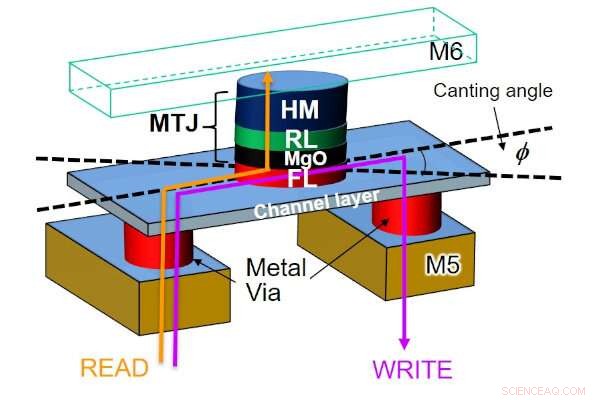

p Um esquema da célula SOT-MRAM (dispositivo de três terminais) Crédito:CIES, Tohoku University

p Um esquema da célula SOT-MRAM (dispositivo de três terminais) Crédito:CIES, Tohoku University

-

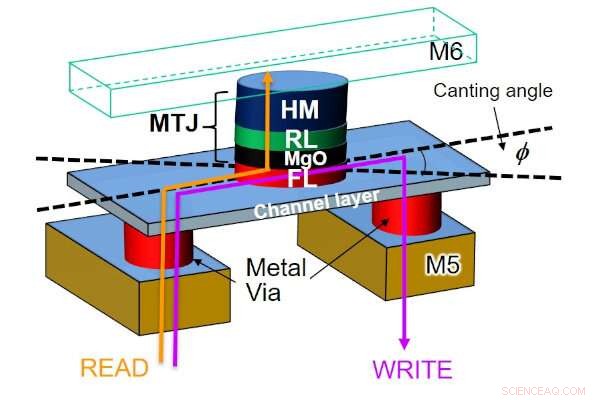

p Uma vista esquemática da célula SOT-MRAM inclinada. Crédito:CIES, Tohoku University

p Uma vista esquemática da célula SOT-MRAM inclinada. Crédito:CIES, Tohoku University

p A equipe de pesquisa liderada pelos professores Tetsuo Endoh e Hideo Ohno - o atual presidente da Tohoku University - desenvolveu um processo de integração para dispositivos SOT compatíveis com a tecnologia CMOS de 55 nm e dispositivos SOT fabricados em substratos CMOS de 300 mm. O dispositivo SOT recentemente desenvolvido alcançou simultaneamente alta velocidade de comutação até 0,35 ns e um fator de estabilidade térmica suficientemente alto (E / k

B T 70) para aplicações de memória não volátil de alta velocidade com robustez contra recozimento a 400 ° C. Com base nessa conquista, a equipe de pesquisa integrou o dispositivo SOT com transistores CMOS e finalmente demonstrou a operação de alta velocidade em células de memória SOT-MRAM completas.

p Essas conquistas abordaram as questões para tornar o SOT-MRAM prático para aplicações comerciais e, assim, oferecer uma maneira de substituir o SRAM por SOT-MRAM, o que contribuirá para a realização de eletrônicos de alto desempenho com baixo consumo de energia.

p Os resultados serão apresentados no Encontro Internacional de Dispositivos Eletrônicos IEEE 2019 em San Francisco, 7 a 11 de dezembro, 2019.