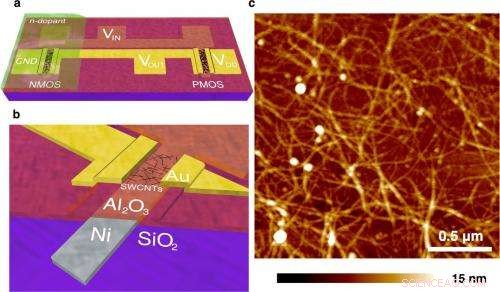

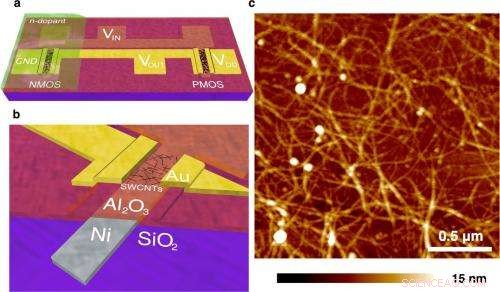

p Ilustrações de (a) o inversor CNT CMOS e (b) uma seção transversal de um transistor CNT individual, incluindo uma porta de Ni de 25 nm de espessura que permite um consumo de energia ultrabaixo. (c) Imagem de microscopia de força atômica da morfologia do filme CNT na região do canal do transistor. Crédito:Geier, et al. © 2013 American Chemical Society

p Ilustrações de (a) o inversor CNT CMOS e (b) uma seção transversal de um transistor CNT individual, incluindo uma porta de Ni de 25 nm de espessura que permite um consumo de energia ultrabaixo. (c) Imagem de microscopia de força atômica da morfologia do filme CNT na região do canal do transistor. Crédito:Geier, et al. © 2013 American Chemical Society

p (Phys.org) —Os pesquisadores demonstraram um novo dispositivo lógico baseado em nanotubos de carbono (CNT) que consome apenas 0,1 nanowatts (nW) em seus estados estáticos LIGADO e DESLIGADO, representando o menor valor relatado em 3 ordens de magnitude para dispositivos lógicos CMOS baseados em CNT. O dispositivo pode servir como um bloco de construção para grandes áreas, circuitos lógicos CNT de potência ultrabaixa que podem ser usados para realizar uma variedade de aplicações de nanoeletrônica. p Os pesquisadores, Michael L. Geier, et al., na Northwestern University em Evanston, Illinois, e a Universidade de Minnesota em Minneapolis, publicaram seu artigo sobre a lógica subnanowatt CNT em uma edição recente da

Nano Letras .

p "Um circuito integrado moderno tem mais de 1 bilhão de transistores, "co-autor Mark C. Hersam, Professor de Ciência e Engenharia de Materiais, Química, e medicina na Northwestern University, contado

Phys.org . "Consequentemente, a dissipação de energia por transistor precisa ser muito baixa para que todo o circuito tenha um consumo de energia razoável. Na verdade, é geralmente aceito que o consumo de energia é o principal fator limitante para alcançar aumentos adicionais na complexidade (ou seja, número de transistores) em circuitos integrados. "

p Como explicam os pesquisadores, uma das maiores vantagens da arquitetura CMOS é que ela tem um consumo de energia intrinsecamente baixo. Esse benefício surge do fato de que, ao contrário de outras arquiteturas lógicas, um dos dois tipos de transistores (tipo p ou tipo n) é desligado sob condições de estado estacionário em cada porta lógica em dispositivos CMOS.

p Para aproveitar ao máximo esse potencial de consumo de energia extremamente baixo, os transistores tipo-p e tipo-n precisam ter tensões de limiar precisamente ajustadas e bem separadas, quais são os níveis de tensão que determinam se o dispositivo está LIGADO ou DESLIGADO. Até aqui, esta questão das tensões de limiar não foi abordada, e os pesquisadores aqui o identificaram como o principal desafio que limita a realização de eletrônicos CMOS baseados em CNT altamente integrados.

p Em seu estudo, os pesquisadores usaram uma estrutura de porta de metal para alcançar tensões de limiar simétricas e claramente separadas para transistores CNT tipo p e tipo n, resultando no consumo de energia ultrabaixo. Nos estados estáticos, em que o dispositivo está LIGADO ou DESLIGADO, o consumo de energia é inferior a 0,1 nW. No ponto médio do estado de transferência, quando ambos os transistores do tipo p e do tipo n estão simultaneamente no estado LIGADO, a tensão atinge seu pico em 10 nW.

p Ao conectar vários transistores CNT em várias configurações, os pesquisadores demonstraram o inversor, Portas lógicas NAND e NOR. No futuro, essas portas podem ser integradas em circuitos complexos, onde eles podem fornecer consumo de energia estática de subnanowatt junto com as outras vantagens dos CNTs, como capacidade de processamento e flexibilidade da solução.

p "Agora estamos trabalhando para fazer circuitos mais complicados, onde teremos substancialmente mais transistores e portas lógicas em cascata, "Hersam disse." Também temos interesse em combinar nanotubos de carbono com outros materiais nanoeletrônicos emergentes em nosso laboratório (por exemplo, dissulfeto de molibdênio [MoS

2 ]). " p © 2013 Phys.org. Todos os direitos reservados.