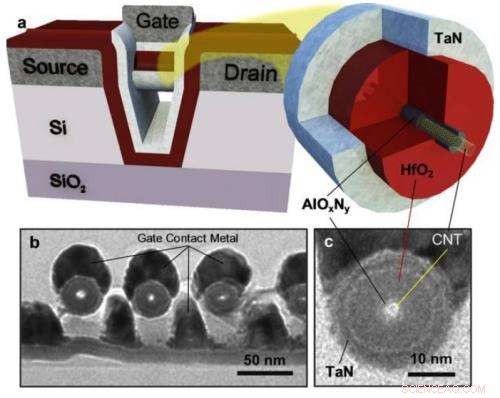

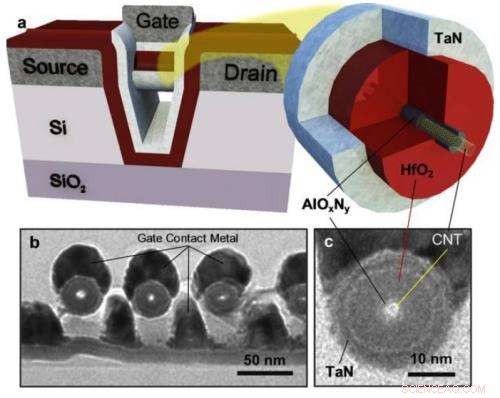

p (a) Diagrama transversal do CNTFET ilustrando como o canal CNT (diagrama em corte mostrado à direita) é suspenso através da vala de silício e contatado em ambos os lados pela fonte / dreno. (b) e (c) mostram imagens TEM em seção transversal de nanotubos com uma geometria de portão all-around, que protege os nanotubos da influência de dispositivos vizinhos e cargas parasitas. Crédito:Franklin, et al. © 2013 American Chemical Society

p (a) Diagrama transversal do CNTFET ilustrando como o canal CNT (diagrama em corte mostrado à direita) é suspenso através da vala de silício e contatado em ambos os lados pela fonte / dreno. (b) e (c) mostram imagens TEM em seção transversal de nanotubos com uma geometria de portão all-around, que protege os nanotubos da influência de dispositivos vizinhos e cargas parasitas. Crédito:Franklin, et al. © 2013 American Chemical Society

p (Phys.org) —Ao longo dos anos 70, Anos 80 e 90, o desempenho do transistor aumentou continuamente de acordo com algumas regras de escala simples. Essas regras postulam que o tamanho do transistor e a tensão de alimentação devem diminuir à medida que a densidade de potência permanece constante, resultando em um aumento geral no desempenho. Contudo, limitações físicas interromperam o dimensionamento da tensão de alimentação no início dos anos 2000, portanto, as regras de escala simples não se aplicam mais. Agora, qualquer aumento no desempenho vem ao custo de um aumento no consumo de energia, de modo que o desempenho do transistor se estabilizou desde meados dos anos 2000. p Agora em um novo estudo, pesquisadores da IBM T.J. Watson Research Center em Yorktown Heights, Nova york, têm aproveitado o potencial dos nanotubos de carbono como uma forma de estender as regras de dimensionamento e alcançar melhorias de desempenho adicionais em transistores. Um dia, transistores feitos de nanotubos de carbono podem formar a espinha dorsal de muitos de nossos dispositivos eletrônicos, incluindo smartphones e tablets.

p A interrupção de escalonamento que os transistores encontraram na última década foi em grande parte devido às características físicas dos próprios transistores, que são transistores de efeito de campo semicondutores de óxido metálico de silício (MOSFETs). Nos últimos anos, pesquisadores investigaram a possibilidade de substituir os MOSFETs por transistores de efeito de campo de nanotubos de carbono (CNTFETs). Esses transistores já demonstraram muitas características atraentes, incluindo bom desempenho em baixas tensões com componentes de canal de menos de 10 nm de comprimento - uma escala que os MOSFETs de silício não podem alcançar fisicamente com bom desempenho.

p "Existem duas razões principais pelas quais os CNTFETs oferecem benefícios que os MOSFETs não podem:1) Os CNTs são semicondutores de corpo ultrafino (~ 1 nm), que permite que eles sejam integrados em dispositivos dimensionados agressivamente sem perder o controle sobre a corrente no canal; e 2) CNTFETs podem operar em baixas tensões de alimentação, o que significa que eles podem fornecer o nível de corrente elétrica necessária para conduzir os circuitos integrados com menos tensão do que os MOSFETs podem alcançar, "o co-autor e pesquisador da IBM Aaron D. Franklin disse

Phys.org . "Por quase uma década, houve pouca ou nenhuma redução na tensão de alimentação para tecnologias MOSFET - CNTFETs são uma das melhores opções para mudar essa tendência. "

p Contudo, para competir com MOSFETS, Os CNTFETs ainda exigem vários avanços importantes, incluindo uma porta escalonável que pode se auto-alinhar aos contatos de fonte e dreno, dispositivos complementares do tipo n e p (que diferem devido à polarização), e compatibilidade com o processamento de fios necessário para construir circuitos.

p Em seu jornal, os pesquisadores atenderam a todos esses três requisitos construindo um transistor CNT com uma porta que circunda completamente o canal CNT. Os pesquisadores explicam que esta geometria de gate-all-around (GAA) é ideal porque protege o CNT do acoplamento aos CNTs vizinhos e de cargas perdidas que chegam muito perto em uma escala tão pequena e causam instabilidade.

p “O maior significado deste trabalho é a implementação de uma porta que envolve completamente os canais CNT cilíndricos, "Franklin disse." Como os nanotubos são apenas moléculas únicas de ~ 1 nm de diâmetro e são feitos de uma única camada de átomos (oco no interior), eles são muito sensíveis a perturbações elétricas em sua vizinhança. Envolvendo cada canal CNT em seu próprio dielétrico e porta de metal, eles ficam isolados de tais perturbações e levam os dispositivos um passo mais perto de uma tecnologia reproduzível e confiável. "

p A comporta envolvente também é autoalinhada com os contatos da fonte e do dreno sem a necessidade de litografia. Como um portão autoalinhado, não se sobrepõe ou se sobrepõe à fonte / dreno, mas se encaixa quase perfeitamente, o que é importante para garantir um bom caminho para o fluxo de carga. Os pesquisadores também podem dimensionar o comprimento do portão para 20 nm, e prever que um escalonamento adicional é possível para canais CNT ainda menores.

p O gate também pode ser usado para realizar dispositivos do tipo n e p usando diferentes materiais dielétricos para alterar a polaridade. Embora o dispositivo tipo n tenha um desempenho melhor do que o dispositivo tipo p, os pesquisadores preveem que o último poderia ser melhorado com regiões espaçadoras mais finas, uma vez que esses espaçadores criam uma barreira para carregar o transporte.

p Os pesquisadores também realizaram simulações quânticas do CNTFET para confirmar sua compreensão do funcionamento do dispositivo. Os resultados da simulação corresponderam de perto aos resultados experimentais, e também permitiu aos pesquisadores projetar o impacto de diferentes variáveis no desempenho do dispositivo, incluindo espessura do espaçador e dopagem. Essas modificações poderiam, teoricamente, aumentar a corrente ativa, diminua a corrente fora do ar, e entregar uma oscilação de sublimiar muito perto do limite teórico de 60 mv / dec, o que significa que o transistor pode alternar muito rapidamente entre os estados ligado e desligado.

p Daqui para frente, os resultados demonstram que matrizes de CNTs podem ser integradas em escalonáveis, transistores autoalinhados do tipo n e p com portas envolventes ideais. Os pesquisadores prevêem que, com mais otimização, esses CNTFETs podem um dia servir como baixa tensão, transistores de alto desempenho que têm amplo impacto em aplicações futuras.

p "Na IBM, mostramos nos últimos anos que você pode alcançar um excelente desempenho de CNTFET em comprimentos de canal abaixo de 10 nm e agora pode fazê-lo em uma estrutura wrap-gate tecnologicamente compatível, "Franklin disse." O maior desafio remanescente no nível do dispositivo é melhorar a injeção de portadores nos contatos de metal-CNT dos dispositivos. Quando os contatos são dimensionados para as pequenas dimensões necessárias para uma tecnologia, a resistência de contato aumenta substancialmente e deve ser tratada. Embora esse problema não seja exclusivo dos CNTFETs (MOSFETs de todos os tipos sofrem de forma semelhante), é um obstáculo que requer uma resolução para acessar todo o potencial de uma tecnologia CNT.

p "Fora da área do dispositivo, os dois maiores obstáculos de materiais são continuar a aumentar a pureza e o isolamento dos CNTs semicondutores de suas contrapartes metálicas e montar com precisão os CNTs em locais precisos em um substrato. Ambas as áreas tiveram um progresso impressionante no último ano, tanto da IBM quanto de outros grupos de pesquisa. " p © 2013 Phys.org. Todos os direitos reservados.