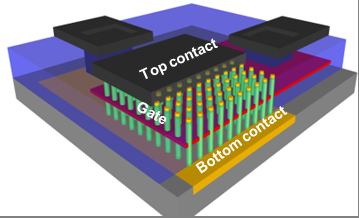

p Diagrama de um nano-transistor 3D mostrando a porta (vermelha) em torno dos nanofios verticais (verde) e separando os contatos nas extremidades de cada nanofio (bege). Crédito:© X-L Han e G. Larrieu

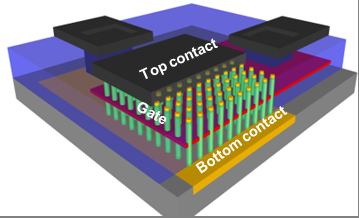

p Diagrama de um nano-transistor 3D mostrando a porta (vermelha) em torno dos nanofios verticais (verde) e separando os contatos nas extremidades de cada nanofio (bege). Crédito:© X-L Han e G. Larrieu

p Um novo avanço poderia empurrar os limites da miniaturização de componentes eletrônicos mais longe do que se pensava ser possível. Uma equipe do Laboratoire d'Analyse et d'Architecture des Systèmes (LAAS) e do Institut d'Électronique, de Microélectronique et de Nanotechnologie (IEMN) construiu um transistor nanométrico que exibe propriedades excepcionais para um dispositivo de seu tamanho. Para alcançar este resultado, os pesquisadores desenvolveram uma nova arquitetura tridimensional que consiste em uma matriz vertical de nanofios cuja condutividade é controlada por um portão medindo apenas 14 nm de comprimento. p Publicado em

Nanoescala , essas descobertas abrem o caminho para alternativas às estruturas planas usadas em microprocessadores e unidades de memória. O uso de transistores 3D pode aumentar significativamente a potência dos dispositivos microeletrônicos.

p Os "blocos de construção" da microeletrônica, transistores consistem em um componente semicondutor, chamado canal, ligando dois terminais. O fluxo de corrente entre esses terminais é controlado por um terceiro terminal, chamado portão. Agindo como um interruptor, a porta determina se o transistor está ligado ou desligado. Nos últimos 50 anos, transistores foram reduzidos constantemente em tamanho, permitindo o desenvolvimento de dispositivos microeletrônicos cada vez mais poderosos. Contudo, é geralmente aceito que os transistores de hoje, com sua arquitetura plana, estão se aproximando do limite da miniaturização:há um tamanho mínimo sob o qual o controle do portão sobre o canal se torna cada vez menos eficaz. Em particular, correntes de fuga começam a interferir nas operações lógicas executadas pelo conjunto de transistores. Para superar esse problema, pesquisadores em todo o mundo estão investigando alternativas que permitirão que a corrida pela miniaturização continue.

p Uma equipe de pesquisadores do LAAS e do IEMN construiu agora o primeiro transistor nanométrico verdadeiramente tridimensional. O dispositivo consiste em um arranjo de nanofios vertical estreito de cerca de 200 nm de comprimento ligando duas superfícies condutoras. Um portão de cromo envolve completamente cada nanofio e controla o fluxo de corrente, resultando em um controle de transistor ideal para um sistema deste tamanho. O portão tem apenas 14 nm de comprimento, em comparação com 28 nm para os transistores nos chips de hoje, mas sua capacidade de controlar a corrente no canal do transistor atende aos requisitos da microeletrônica contemporânea.

p Essa arquitetura pode levar ao desenvolvimento de microprocessadores nos quais os transistores são empilhados. O número de transistores em um determinado espaço poderia, portanto, ser aumentado consideravelmente, junto com a capacidade de desempenho de microprocessadores e unidades de memória. Outra vantagem significativa desses componentes é que eles são relativamente simples de fabricar e não requerem litografia de alta resolução. Além disso, esses transistores 3D poderiam ser facilmente integrados aos dispositivos microeletrônicos convencionais usados pela indústria hoje.

p Uma patente foi registrada para esses transistores. Os pesquisadores agora planejam continuar seus esforços para reduzir ainda mais o tamanho do portão, que eles acreditam que poderia ser menor do que 10 nm, mas ainda fornecendo controle satisfatório sobre o transistor. Além disso, a equipe está procurando parceiros industriais para ajudar a projetar os dispositivos eletrônicos do futuro usando a arquitetura 3D desses novos transistores.