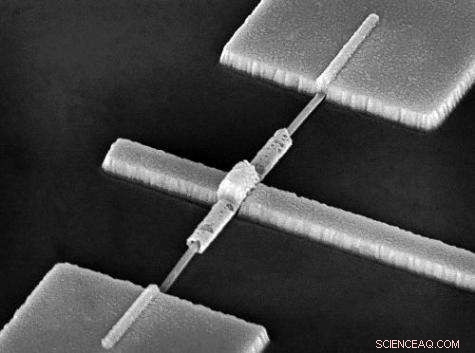

p Uma micrografia eletrônica de varredura do transistor de nanofio horizontal wrap-gate. Imagem cortesia de Adam Micolich.

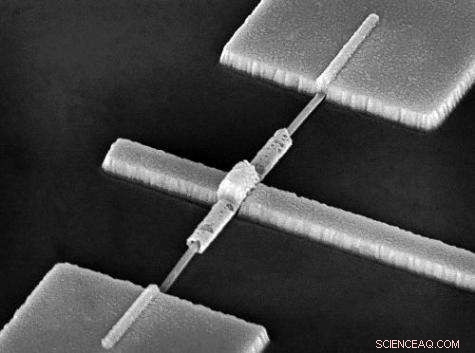

p Uma micrografia eletrônica de varredura do transistor de nanofio horizontal wrap-gate. Imagem cortesia de Adam Micolich.

p (PhysOrg.com) - Em um feito interessante de engenharia em nanoescala, pesquisadores da Lund University na Suécia e da University of New South Wales fizeram o primeiro transistor nanofio apresentando um metal concêntrico 'wrap-gate' que fica horizontalmente em um substrato de silício. p Dois aspectos notáveis de seu design são a simplicidade de fabricação e a capacidade única de ajustar o comprimento do wrap-gate por meio de uma única etapa de gravação úmida, observa o professor associado Adam Micolich, um ARC Future Fellow no Grupo de Nanoeletrônica na UNSW School of Physics.

p Empacotar densidades cada vez maiores de transistores em um microchip tem um preço alto - a sobreposição reduzida entre o canal semicondutor através do qual a corrente flui e a porta de metal torna mais difícil ligar e desligar a corrente.

p Isso levou ao desenvolvimento do 'Transistor de Efeito de Campo Fin', ou FinFET, onde o silício de cada lado do canal é gravado para criar uma estrutura de mesa elevada. Isso permite que o portão se dobre nas laterais do canal, melhorando a comutação sem aumentar o espaço do chip necessário para o dispositivo. Um controle ainda melhor pode ser obtido envolvendo o gate em todo o canal. Mas colocar metal sob o canal sem comprometer o dispositivo pode ser uma tarefa formidável usando técnicas convencionais de microfabricação de silício "de cima para baixo".

p Isso levou a um interesse significativo em nanofios automontados para aplicações de computação (ver D.K. Ferry, doi:10.1126 / science.1154446). Essas minúsculas agulhas semicondutoras, cerca de 50 nm de diâmetro e até vários mícrons de comprimento, são cultivados usando deposição de vapor químico e posicionados verticalmente em um substrato semicondutor, tornando possível depositar um isolador e porta de metal em torno de toda a superfície externa do nanofio.

p Embora esses nanofios revestidos possam ser transformados em transistores totalmente funcionais na orientação vertical, o processo para conseguir isso é muito complicado. E em muitos casos, é mais desejável ter o transistor de nanofio deitado no substrato, como acontece com os transistores de silício convencionais. Isso representa um desafio interessante para os nanotecnologistas:É possível fazer transistores de nanofios com um 'wrap-gate' de metal completo que fica plano em um substrato semicondutor?

p Em trabalho publicado esta semana em

Nano Letras [Tempestade

et al . doi:10.1021 / nl104403g], a equipe não apenas demonstra os primeiros transistores de nanofios tipo wrap-gate horizontal, mas eles demonstram que podem ser feitos usando um processo extremamente simples que lhes permite definir com precisão o comprimento do wrap-gate usando uma única etapa de gravação úmida, sem qualquer necessidade de litografia adicional.

p Sua abordagem explora a capacidade da solução de decapagem de minar a resistência e decapagem ao longo do nanofio, produzindo portas que variam em comprimento de um pouco menos do que a separação de contato a tão baixo quanto 100 nm, simplesmente ajustando a concentração do condicionador. Os dispositivos resultantes têm excelente desempenho elétrico e podem ser produzidos de forma confiável com alto rendimento.

p Além de ser um avanço significativo nas técnicas de nanofabricação, esses dispositivos abrem novos caminhos interessantes para a pesquisa fundamental.

p Os nanofios wrap-gated são ideais para estudos de transporte quântico unidimensional em semicondutores, onde fenômenos notáveis como cristalização de elétrons e separação de carga de spin podem ser observados. Adicionalmente, o forte acoplamento portão-canal combinado com uma superfície envolvida de ouro exposta oferece potencial interessante para aplicações de detecção, utilizando a química estabelecida para anticorpos e outros polipeptídeos de ligação a superfícies de ouro.