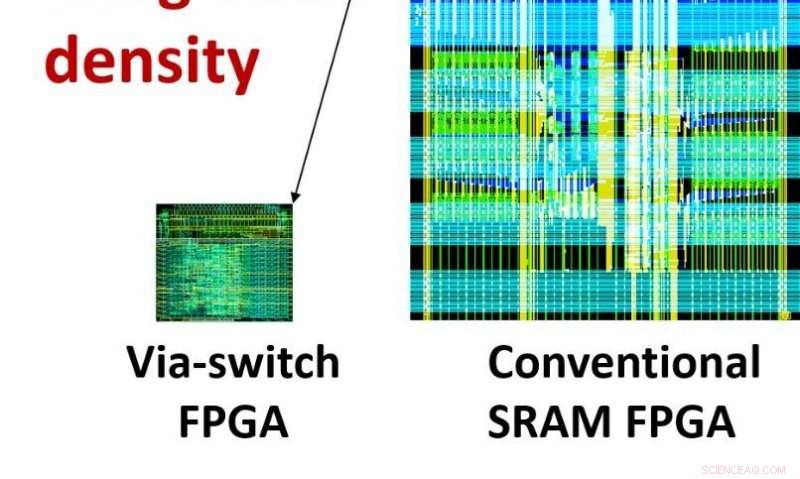

Fig. 1:Densidade de integração aprimorada:Comparação na densidade de integração. Crédito:IEEE International Solid-State Circuits Conference

Cientistas da Universidade de Osaka construíram um novo dispositivo de computação a partir de matrizes de portas programáveis em campo (FPGA) que podem ser personalizadas pelo usuário para obter o máximo de eficiência em aplicações de inteligência artificial. Comparado com o hardware religável usado atualmente, o sistema aumenta a densidade do circuito por um fator de 12. Além disso, espera-se que reduza o uso de energia em 80%. Esse avanço pode levar a soluções de inteligência artificial (IA) flexíveis que fornecem desempenho aprimorado enquanto consomem muito menos eletricidade.

A IA está se tornando parte da vida cotidiana de quase todos os consumidores. Aplicativos de smartphone para compartilhamento de carona, como o Uber, Filtros de spam do Gmail, e dispositivos de casa inteligente, como Siri e Nest, todos dependem de IA. Contudo, implementar esses algoritmos muitas vezes requer uma grande quantidade de capacidade de computação, o que significa grandes contas de eletricidade, bem como grandes pegadas de carbono. Os sistemas que poderiam ser reconectados para otimizar os circuitos do computador para cada tarefa, como o cérebro humano, forneceriam uma eficiência energética bastante aprimorada.

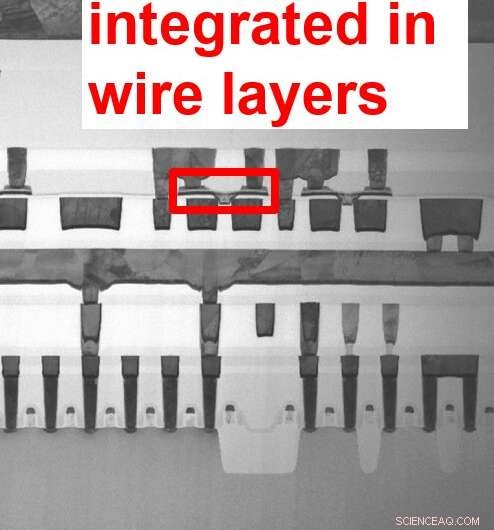

Normalmente, pensamos em hardware, que inclui as portas lógicas físicas e transistores do processador de um computador, conforme fixado pelo fabricante. Contudo, As matrizes de portas programáveis em campo são elementos lógicos especializados que podem ser reconectados em campo pelo usuário para aplicações lógicas personalizadas. A equipe de pesquisa usou "interruptores via" não voláteis que permanecem conectados até que o usuário decida reconfigurá-los. Usando novos métodos de nanofabricação, eles foram capazes de compactar 12 vezes mais elementos em um layout de "barra transversal" semelhante a uma grade. Ao reduzir a distância, os sinais eletrônicos precisam ser roteados, os aparelhos acabaram precisando de 80% menos energia.

Fig. 2:Seção transversal de interconexão do FPGA via switch desenvolvido. Crédito:IEEE International Solid-State Circuits Conference

"Nosso sistema baseado em matrizes de portas programáveis em campo tem um ciclo de design muito rápido. Ele pode ser reprogramado diariamente, se desejado, para obter o máximo de poder de computação para cada nova aplicação de IA, “O primeiro autor, Masanori Hashimoto, diz. O uso de via-switches também elimina a necessidade da área de silício de programação que era necessária nos dispositivos FPGA anteriores.

"Via-switch FPGA é adequado como uma plataforma de implementação de alto desempenho dos algoritmos de AI mais recentes, "diz o autor sênior Jaehoon Yu.

O artigo, "Via-switch FPGA:implementação de CMOS de 65 nm e extensão de arquitetura para aplicações de IA, "foi publicado nos resumos técnicos da IEEE International Solid-State Circuits Conference 2020.