Crédito:Samsung

"O processo nanométrico lida com o espaço entre os transistores montados em um substrato em um nível nanométrico, " disse Pulso .

"Quanto menor a distância, mais chips podem ser espremidos para aumentar o poder de computação e a eficiência energética. Um nanômetro corresponde a um décimo milésimo do diâmetro de um cabelo humano. "

No Samsung Foundry Forum em Santa Clara, Califórnia, a empresa recentemente procurou impressionar os avanços que fez no desenvolvimento de processos de gate-all-around (GAA) de 3 nm.

A Samsung Foundry agora apresenta o MBCFET (FET de canal de várias pontes). Isso consiste em nanofolhas empilhadas. Com a formação da nanofolha, uma corrente maior por pilha é alcançável, disse SamMobile .

ExtremeTech descreveu o anúncio como sendo sobre "um novo, arquitetura de transistor evoluída "saindo da Samsung Foundry - envolvendo a abordagem de" nanofolhas "para seu nó de 3 nm.

(Da redação da Samsung:"O GAA convencional baseado em nanofios requer um número maior de pilhas devido à sua pequena largura efetiva de canal. Por outro lado, Versão patenteada do GAA pela Samsung, MBCFET (FET Multi-Bridge-Channel), usa uma arquitetura de nanosheet, permitindo maior corrente por pilha. ")

O blog CNXSoft lançou ainda mais luz sobre o motivo da transição de nanofios para nanofolhas.

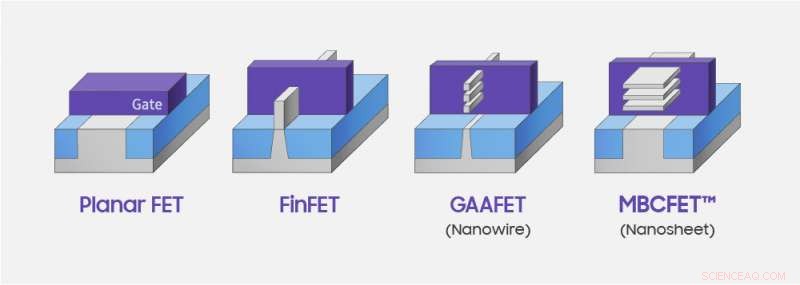

"Frequentemente lemos que novos processadores são fabricados com um processo FinFET. O novo processo foi criado devido aos efeitos de canal curto em transistores planares tradicionais, e FinFET (transistor de efeito de campo Fin) foi introduzido para permitir escalonamento de tensão adicional, mas com o nó de processo se tornando cada vez menor, efeitos eletrostáticos começaram a causar problemas. "

O uso de nanofios GAA (Gate All Around) para limitar esses efeitos foi considerado uma resposta, mas esses são aparentemente muito difíceis de integrar ao silício, disse o blog, então a Samsung acabou usando camadas finas (nanofolhas) em vez de nanofios, "permitindo maior corrente por trilha em sua implementação GAA chamada MBCFET (Multi-Bridge Channel Field-Effect Transistor)."

Para quem precisa processar a sobrecarga de siglas, Ramish Zafar em Wccftech levou seus leitores ao longo da jornada Samsung. 1. A Samsung colaborou com a IBM para nós de processo GAAFET (Gate-All-Around). 2. Agora, a empresa anunciou suas personalizações para o processo anterior, e este é o MBCFET.

Zafar tinha mais a dizer sobre o MBCET. "Ao contrário dos designs FinFET tradicionais, O GAAFET permite que o material do gate envolva o canal de todos os lados. A Samsung afirma que o design do MBCFET melhorará o comportamento liga-desliga do processo, e permite que os processadores reduzam a tensão operacional abaixo de 0,75 V. Um ponto crucial para o MBCFET é que o processo é totalmente compatível com os designs do FinFET e não requer nenhuma ferramenta nova para a fabricação. "

Crédito:Samsung

Quão, no entanto, todas essas boas notícias figuram nos planos de desenvolvimento da empresa. Quando podemos esperar ver a tecnologia em ação? Joel Hruska abordou isso em ExtremeTech .

"Em seu Samsung Foundry Forum esta semana, A Samsung declarou que seu kit de design de produto para chips de 3 nm está agora em alfa, tendo atingido o marco de desenvolvimento de 0.1. A Samsung está planejando lançar uma infinidade de nós de processo nos próximos anos, com faixas de desenvolvimento planejadas para 7 nm, 6 nm, 5nm, 4nm, e sim, 3 nm. "

Hruska acrescentou, "As melhorias para 3nm em comparação com 7nm são bastante boas, mas este nó não será lançado por um bom tempo. "Seu artigo traz um gráfico que mostra a progressão conforme comunicado pela Samsung.

© 2019 Science X Network