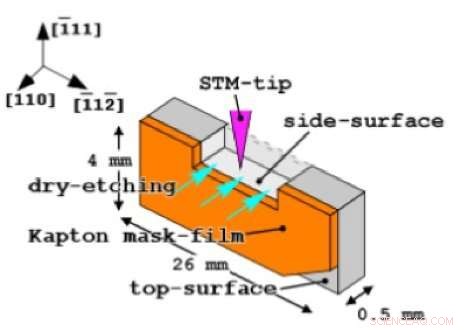

Figura 1. Um esquema de uma amostra de Si (110) com uma máscara de filme Kapton:corrosão seca da (110) superfície superior e ponta STM se aproximando da superfície lateral (-111). Crédito:Universidade de Osaka

Uma colaboração de pesquisa entre a Universidade de Osaka e o Instituto de Ciência e Tecnologia de Nara pela primeira vez usou microscopia de tunelamento de varredura (STM) para criar imagens de superfícies laterais atomicamente planas de cristais de silício 3-D. Este trabalho ajuda os fabricantes de semicondutores a continuar a inovar enquanto produzem menores, mais rápido, e chips de computador mais eficientes em termos de energia para computadores e smartphones.

Nossos computadores e smartphones são carregados com milhões de minúsculos transistores. A velocidade de processamento desses dispositivos aumentou dramaticamente com o tempo, à medida que o número de transistores que cabem em um único chip de computador continua a aumentar. Com base na Lei de Moore, o número de transistores por chip dobrará a cada 2 anos, e nesta área parece estar se segurando. Para manter esse ritmo de inovação rápida, os fabricantes de computadores estão continuamente em busca de novos métodos para tornar cada transistor cada vez menor.

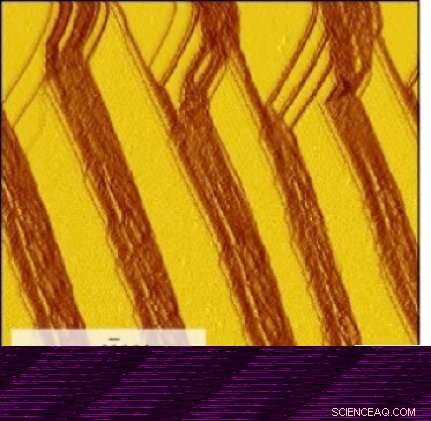

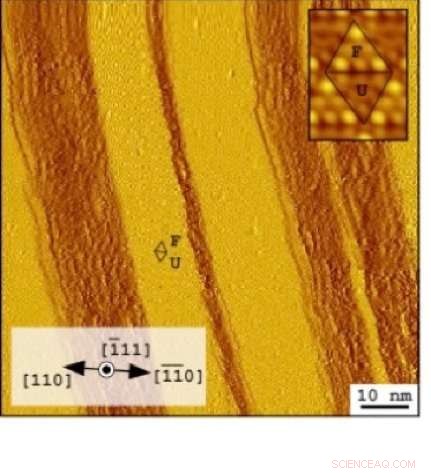

Figura 3. Imagens STM derivadas espaciais com 200x200 nm ^ 2 em Vs =+1,5 V. Terraços planos tornam-se mais brilhantes e as bordas mais escuras. A direção do andar de baixo vai da esquerda ((110) superfície superior) para a direita ((-1-10) superfície posterior). Crédito:Universidade de Osaka

Os microprocessadores atuais são feitos adicionando padrões de circuitos a wafers planos de silício. Uma nova maneira de empilhar mais transistores no mesmo espaço é fabricar estruturas 3-D. Transistores de efeito de campo do tipo barbatana (FETs) são nomeados assim porque têm estruturas de silício semelhantes a barbatanas que se estendem para o ar, fora da superfície do chip. Contudo, este novo método requer um cristal de silício com um topo e superfícies laterais perfeitamente planas, em vez de apenas a superfície superior, como acontece com os dispositivos atuais. Projetar a próxima geração de chips exigirá um novo conhecimento das estruturas atômicas das superfícies laterais.

Figura 3. Imagens STM derivadas espaciais com 200x200 nm ^ 2 em Vs =+1,5 V. Terraços planos tornam-se mais brilhantes e as bordas mais escuras. A direção do andar de baixo vai da esquerda ((110) superfície superior) para a direita ((-1-10) superfície posterior). Crédito:Universidade de Osaka

Agora, pesquisadores da Universidade de Osaka e do Instituto de Ciência e Tecnologia de Nara relatam que usaram o STM para obter imagens da superfície lateral de um cristal de silício pela primeira vez. STM é uma técnica poderosa que permite que as localizações dos átomos de silício individuais sejam vistas. Ao passar uma ponta afiada muito perto da amostra, elétrons podem saltar através da lacuna e criar uma corrente elétrica. O microscópio monitorou esta corrente, e determinou a localização dos átomos na amostra.

"Nosso estudo é um grande primeiro passo em direção à avaliação resolvida atomicamente de transistores projetados para ter formatos 3-D, "diz a co-autora do estudo, Azusa Hattori.

Para tornar as superfícies laterais o mais lisas possível, os pesquisadores primeiro trataram os cristais com um processo chamado corrosão iônica reativa. O co-autor Hidekazu Tanaka diz:"Nossa capacidade de olhar diretamente para as superfícies laterais usando STM prova que podemos fazer estruturas tridimensionais artificiais com um ordenamento de superfície atômica quase perfeito."