Novo chip neuromórfico para IA de ponta, com uma pequena fração da energia e tamanho das plataformas de computação atuais

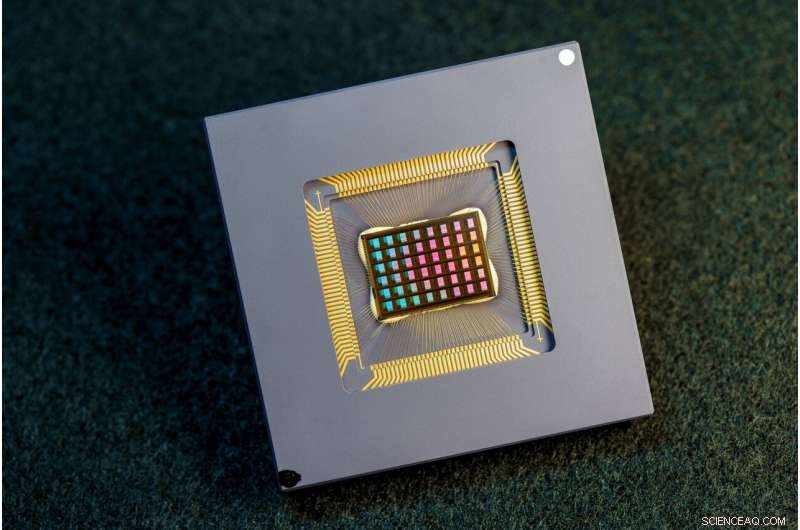

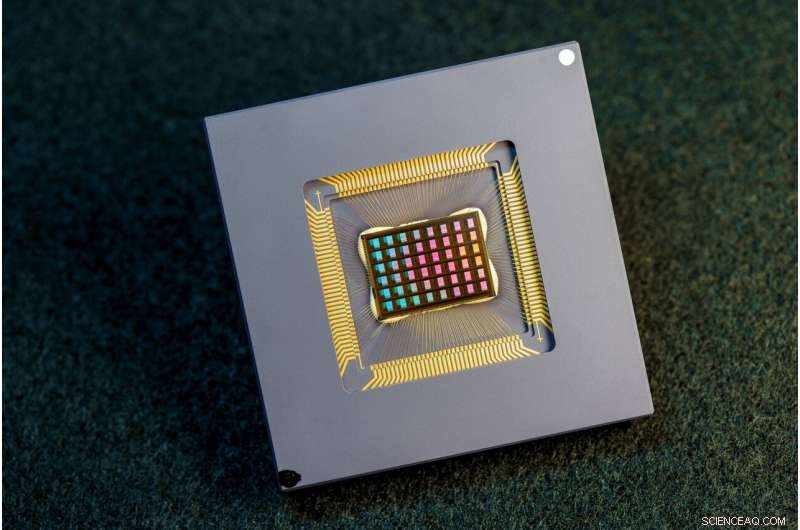

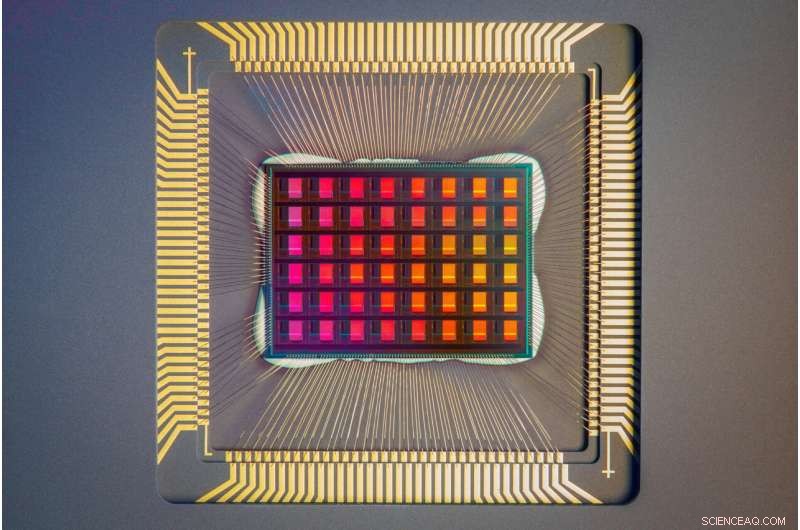

Uma equipe de pesquisadores internacionais projetou, fabricou e testou o chip NeuRRAM. Crédito:David Baillot/Universidade da Califórnia San Diego

Uma equipe internacional de pesquisadores projetou e construiu um chip que executa cálculos diretamente na memória e pode executar uma ampla variedade de aplicativos de IA – tudo com uma fração da energia consumida pelas plataformas de computação para computação de IA de uso geral.

O chip neuromórfico NeuRRAM aproxima a IA da execução em uma ampla variedade de dispositivos de borda, desconectados da nuvem, onde eles podem executar tarefas cognitivas sofisticadas em qualquer lugar e a qualquer momento, sem depender de uma conexão de rede com um servidor centralizado. Os aplicativos são abundantes em todos os cantos do mundo e em todas as facetas de nossas vidas, e variam de relógios inteligentes a fones de ouvido VR, fones de ouvido inteligentes, sensores inteligentes em fábricas e rovers para exploração espacial.

O chip NeuRRAM não é apenas duas vezes mais eficiente em termos de energia do que os chips "compute-in-memory" de última geração, uma classe inovadora de chips híbridos que executam cálculos na memória, mas também fornece resultados tão precisos quanto chips digitais convencionais. As plataformas convencionais de IA são muito mais volumosas e normalmente são restritas ao uso de grandes servidores de dados operando na nuvem.

Além disso, o chip NeuRRAM é altamente versátil e suporta muitos modelos e arquiteturas de redes neurais diferentes. Como resultado, o chip pode ser usado para muitas aplicações diferentes, incluindo reconhecimento e reconstrução de imagem, bem como reconhecimento de voz.

"A sabedoria convencional é que a maior eficiência da computação na memória é à custa da versatilidade, mas nosso chip NeuRRAM obtém eficiência sem sacrificar a versatilidade", disse Weier Wan, o primeiro autor correspondente do artigo e um recente Ph.D. graduado da Universidade de Stanford que trabalhou no chip enquanto estava na UC San Diego, onde foi co-orientado por Gert Cauwenberghs no Departamento de Bioengenharia.

A equipe de pesquisa, co-liderada por bioengenheiros da Universidade da Califórnia em San Diego, apresenta seus resultados na edição de 17 de agosto da

Nature .

Atualmente, a computação de IA consome muita energia e é computacionalmente cara. A maioria dos aplicativos de IA em dispositivos de borda envolve a movimentação de dados dos dispositivos para a nuvem, onde a IA os processa e analisa. Em seguida, os resultados são movidos de volta para o dispositivo. Isso ocorre porque a maioria dos dispositivos de borda é alimentada por bateria e, como resultado, possui apenas uma quantidade limitada de energia que pode ser dedicada à computação.

Ao reduzir o consumo de energia necessário para inferência de IA na borda, esse chip NeuRRAM pode levar a dispositivos de borda mais robustos, inteligentes e acessíveis e a uma fabricação mais inteligente. Também pode levar a uma melhor privacidade de dados, pois a transferência de dados de dispositivos para a nuvem traz maiores riscos de segurança.

Em chips de IA, mover dados da memória para unidades de computação é um grande gargalo.

"É o equivalente a fazer uma viagem de oito horas para um dia de trabalho de duas horas", disse Wan.

Para resolver esse problema de transferência de dados, os pesquisadores usaram o que é conhecido como memória resistiva de acesso aleatório, um tipo de memória não volátil que permite a computação diretamente na memória, em vez de em unidades de computação separadas. RRAM e outras tecnologias de memória emergentes usadas como matrizes de sinapses para computação neuromórfica foram pioneiras no laboratório de Philip Wong, consultor de Wan em Stanford e um dos principais contribuintes para este trabalho. A computação com chips RRAM não é necessariamente nova, mas geralmente leva a uma diminuição na precisão dos cálculos realizados no chip e à falta de flexibilidade na arquitetura do chip.

"Compute-in-memory tem sido uma prática comum na engenharia neuromórfica desde que foi introduzida há mais de 30 anos", disse Cauwenberghs. "O que há de novo com o NeuRRAM é que a extrema eficiência agora vem junto com grande flexibilidade para diversos aplicativos de IA com quase nenhuma perda de precisão em plataformas digitais de computação de uso geral padrão."

Uma metodologia cuidadosamente elaborada foi fundamental para o trabalho com vários níveis de "co-otimização" nas camadas de abstração de hardware e software, desde o design do chip até sua configuração para executar várias tarefas de IA. Além disso, a equipe se certificou de considerar várias restrições que vão desde a física do dispositivo de memória até os circuitos e a arquitetura de rede.

"Este chip agora nos fornece uma plataforma para resolver esses problemas em toda a pilha, de dispositivos e circuitos a algoritmos", disse Siddharth Joshi, professor assistente de ciência da computação e engenharia da Universidade de Notre Dame, que começou a trabalhar no projeto como um Ph.D. estudante e pesquisador de pós-doutorado no laboratório Cauwenberghs na UC San Diego.

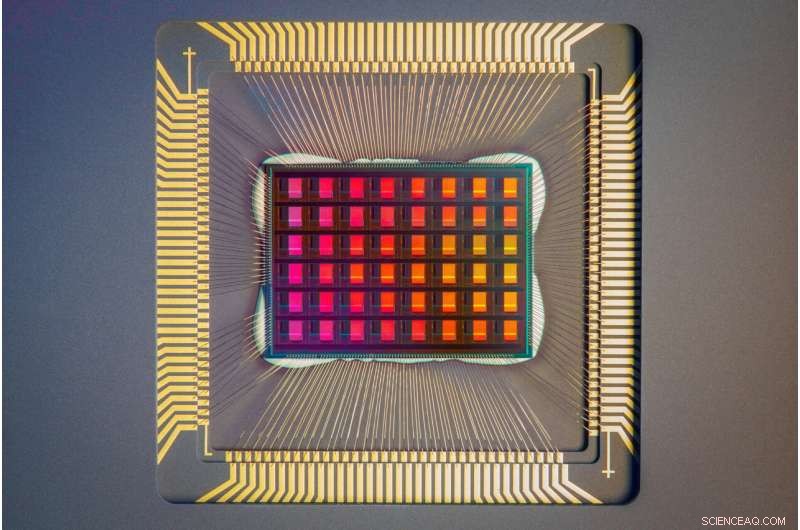

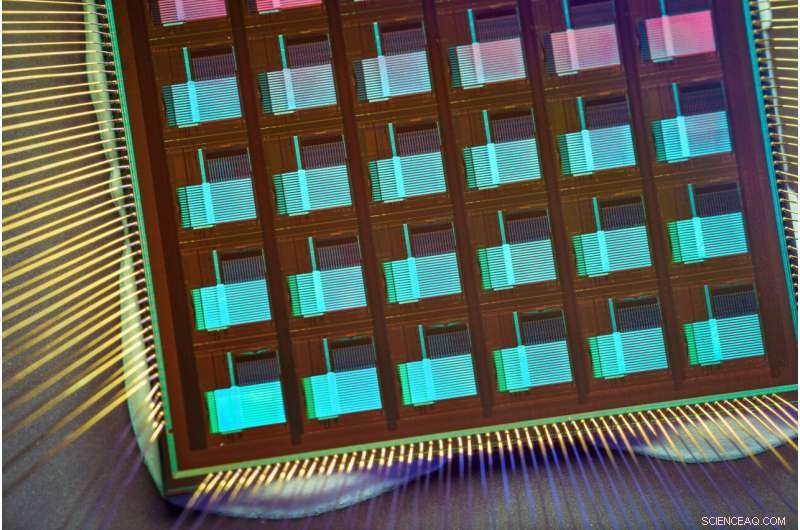

Um close-up do chip NeuRRAM. Crédito:David Baillot/Universidade da Califórnia San Diego

Desempenho do chip Os pesquisadores mediram a eficiência energética do chip por uma medida conhecida como produto de atraso de energia, ou EDP. A EDP combina a quantidade de energia consumida para cada operação e a quantidade de vezes que leva para concluir a operação. Por essa medida, o chip NeuRRAM atinge EDP de 1,6 a 2,3 vezes menor (menor é melhor) e densidade computacional de 7 a 13 vezes maior do que os chips de última geração.

Os pesquisadores executaram várias tarefas de IA no chip. Ele alcançou 99% de precisão em uma tarefa de reconhecimento de dígitos manuscritos; 85,7% em tarefa de classificação de imagens; e 84,7% em uma tarefa de reconhecimento de comando de fala do Google. Além disso, o chip também obteve uma redução de 70% no erro de reconstrução de imagem em uma tarefa de recuperação de imagem. Esses resultados são comparáveis aos chips digitais existentes que realizam computação com a mesma precisão de bits, mas com economias drásticas de energia.

Os pesquisadores apontam que uma das principais contribuições do artigo é que todos os resultados apresentados são obtidos diretamente no hardware. Em muitos trabalhos anteriores de chips de computação em memória, os resultados de benchmark de IA eram frequentemente obtidos parcialmente por simulação de software.

Os próximos passos incluem melhorar arquiteturas e circuitos e dimensionar o projeto para nós de tecnologia mais avançada. Researchers also plan to tackle other applications, such as spiking neural networks.

"We can do better at the device level, improve circuit design to implement additional features and address diverse applications with our dynamic NeuRRAM platform," said Rajkumar Kubendran, an assistant professor for the University of Pittsburgh, who started work on the project while a Ph.D. student in Cauwenberghs' research group at UC San Diego.

In addition, Wan is a founding member of a startup that works on productizing the compute-in-memory technology. "As a researcher and an engineer, my ambition is to bring research innovations from labs into practical use," Wan said.

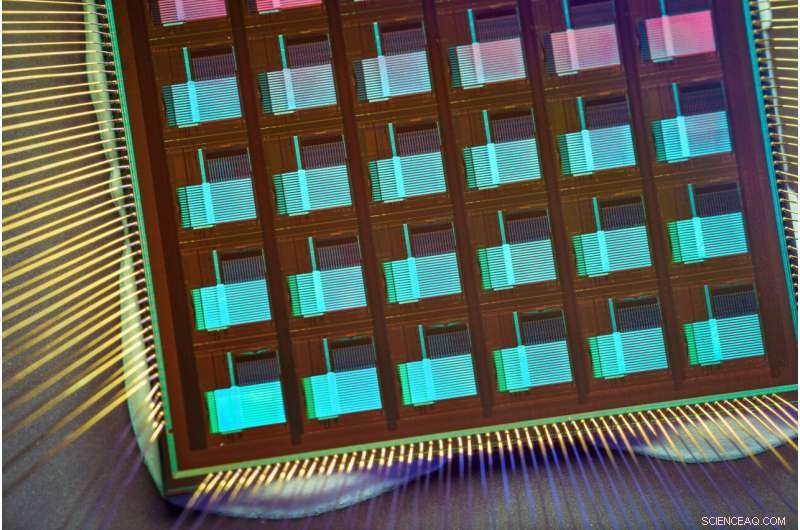

New architecture The key to NeuRRAM's energy efficiency is an innovative method to sense output in memory. Conventional approaches use voltage as input and measure current as the result. But this leads to the need for more complex and more power hungry circuits. In NeuRRAM, the team engineered a neuron circuit that senses voltage and performs analog-to-digital conversion in an energy efficient manner. This voltage-mode sensing can activate all the rows and all the columns of an RRAM array in a single computing cycle, allowing higher parallelism.

In the NeuRRAM architecture, CMOS neuron circuits are physically interleaved with RRAM weights. It differs from conventional designs where CMOS circuits are typically on the peripheral of RRAM weights.The neuron's connections with the RRAM array can be configured to serve as either input or output of the neuron. This allows neural network inference in various data flow directions without incurring overheads in area or power consumption. This in turn makes the architecture easier to reconfigure.

To make sure that accuracy of the AI computations can be preserved across various neural network architectures, researchers developed a set of hardware algorithm co-optimization techniques. The techniques were verified on various neural networks including convolutional neural networks, long short-term memory, and restricted Boltzmann machines.

As a neuromorphic AI chip, NeuroRRAM performs parallel distributed processing across 48 neurosynaptic cores. To simultaneously achieve high versatility and high efficiency, NeuRRAM supports data-parallelism by mapping a layer in the neural network model onto multiple cores for parallel inference on multiple data. Also, NeuRRAM offers model-parallelism by mapping different layers of a model onto different cores and performing inference in a pipelined fashion.

The NeuRRAM chip uses an innovative architecture that has been co-optimized across the stack. Crédito:David Baillot/Universidade da Califórnia San Diego

An international research team The work is the result of an international team of researchers.

The UC San Diego team designed the CMOS circuits that implement the neural functions interfacing with the RRAM arrays to support the synaptic functions in the chip's architecture, for high efficiency and versatility. Wan, working closely with the entire team, implemented the design; characterized the chip; trained the AI models; and executed the experiments. Wan also developed a software toolchain that maps AI applications onto the chip.

The RRAM synapse array and its operating conditions were extensively characterized and optimized at Stanford University.

The RRAM array was fabricated and integrated onto CMOS at Tsinghua University.

The Team at Notre Dame contributed to both the design and architecture of the chip and the subsequent machine learning model design and training.

+ Explorar mais A four-megabit nvCIM macro for edge AI devices