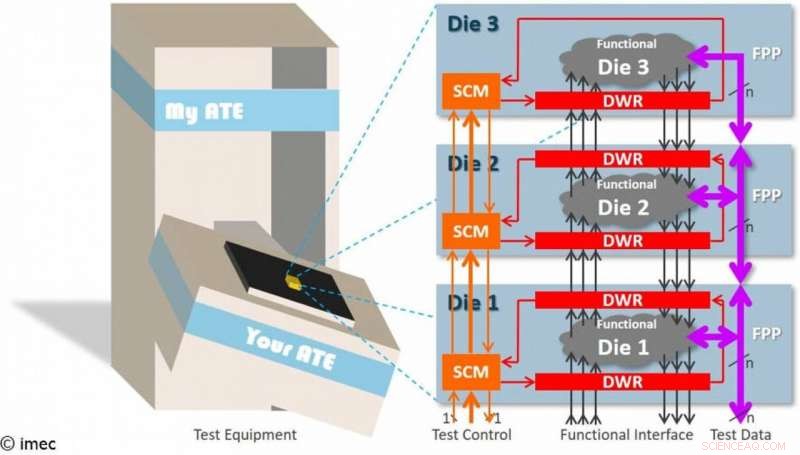

Seção transversal conceitual de um 3D-IC consistindo de três matrizes empilhadas. O equipamento de teste envia estímulos de teste e recebe respostas de teste da interface externa do 3D-IC localizada na parte inferior da pilha. Os elementos de projeto para teste IEEE Std 1838 ™ -2019 nas várias matrizes formam uma arquitetura de acesso de teste consistente por meio da qual o equipamento de teste pode acessar cada matriz na pilha. Crédito:IMEC

Esta semana, IMEC, um centro de pesquisa e inovação líder mundial em nanoeletrônica e tecnologias digitais, anunciou que o IEEE Std 1838TM-2019 - recentemente aprovado pela IEEE Standards Association - será incluído na Biblioteca Digital IEEE Xplore de fevereiro de 2020 em diante. O novo padrão permite que os fabricantes de matrizes projetem matrizes que, se compatível com este padrão, constituir, uma vez empilhado em um 3-D-IC por um integrador de pilha, uma arquitetura de acesso de teste de nível de pilha consistente. O esforço de padronização do 3-D-DfT (design-for-test) foi iniciado pelo IMEC.

3-D-ICs exploram a dimensão vertical para integração adicional, empilhando matrizes umas sobre as outras como uma forma de manter o ímpeto da Lei de Moore. Eric Beyne, bolsista e diretor de programa 3-D System Integration no IMEC, diz, "Os avanços nas tecnologias de processamento de wafer e montagem de pilha estão criando uma grande variedade de arquiteturas de pilha diferentes. Isso causa um aumento acentuado no número de momentos potenciais em que os testes de defeitos de fabricação podem ser executados:pré-ligação (antes do empilhamento), mid-bond (em pilhas parciais), pós-ligação (em pilhas completas), e teste final (em ICs 3-D embalados). O equipamento de teste entra em contato com os ICs por meio de sua interface externa por meio de agulhas de sonda ou no soquete de teste. Em uma pilha de dados, essa interface externa normalmente reside na matriz inferior da pilha. Para que o equipamento de teste seja capaz de fornecer estímulos de teste e receber respostas das várias matrizes na pilha, a colaboração das matrizes subjacentes é necessária para fornecer acesso de teste à matriz que está sendo testada atualmente. "

Um grupo de trabalho IEEE para padronizar 3-D-DfT foi fundado em 2011 por Erik Jan Marinissen, diretor científico do IMEC em Leuven, Bélgica e ele serviu como seu primeiro presidente. Nos últimos anos, Adam Cron, principal engenheiro de P&D no Grupo de Design da Synopsys, tem sido a força motriz como o atual presidente do Grupo de Trabalho.

Amit Sanghani, vice-presidente de engenharia do Grupo de Design da Synopsys em Mountain View, Califórnia, Os EUA declararam:"3-D-IC é uma tecnologia importante para entregar a próxima onda de inovação conforme a escala da indústria passa de 7 nm. Atualmente, O dado pode vir de fornecedores diferentes com arquiteturas DfT desconexas.

O novo padrão consiste em três elementos principais. (1) DWR, o registro do invólucro da matriz:escaneia as cadeias no limite de cada matriz na pilha para permitir o teste modular das partes internas de cada matriz e das interconexões entre cada par de matrizes adjacentes. (2) SCM, o mecanismo de controle serial:um mecanismo de controle de teste de um único bit que transporta instruções para a pilha para controlar os modos de teste dos vários invólucros de dados. (3) FPP, a porta paralela flexível opcional, ou seja, um mecanismo escalonável de acesso de teste de vários bits para transportar com eficiência para cima e para baixo na pilha de matrizes os grandes volumes de dados normalmente associados ao teste de produção. Embora DWR e SCM sejam baseados em padrões DfT existentes, o FPP é verdadeiramente novo para o IEEE Std 1838.

Wolfgang Meyer, diretor de grupo sênior de P&D da Cadence Design Systems em San Jose, Califórnia, NÓS., diz, "Um padrão DfT como o IEEE Std 1838 é importante para a indústria. Os fabricantes de matrizes sabem o que devem fornecer, e os integradores de pilha sabem o que podem esperar. Além disso, Os fornecedores de EDA, como a Cadence, podem concentrar seu suporte de ferramenta em arquiteturas que estão em conformidade com o novo padrão. É bom que haja alguma escalabilidade definida pelo usuário com o padrão, já que o campo 3-D-IC é tão amplo - um padrão rígido de 'tamanho único' não funcionaria. "

Junlin Huang, gerente de uma forte equipe de DfT de 150 pessoas da HiSilicon em Shenzhen, China, diz, "Por ano, fazemos inserção DfT e geração automática de padrão de teste (ATPG) para dezenas de designs de chips digitais muito grandes e complexos nas tecnologias mais avançadas. Agora, esses produtos começam a usar tecnologia 3-D e minha equipe de DfT precisa estar pronta para lidar com os desafios de DfT e ATPG associados. IEEE Std 1838 nos ajudará nessa tarefa. "

De fevereiro de 2020 em diante, o novo padrão IEEE Std 1838 estará disponível via IEEE Xplore para assinantes dos padrões IEEE, bem como para compra para todos os outros.