A equipe NUS Green IC:Dr. Orazio Aiello (à esquerda) e o Professor Associado Massimo Alioto (à direita). Crédito:Universidade Nacional de Cingapura

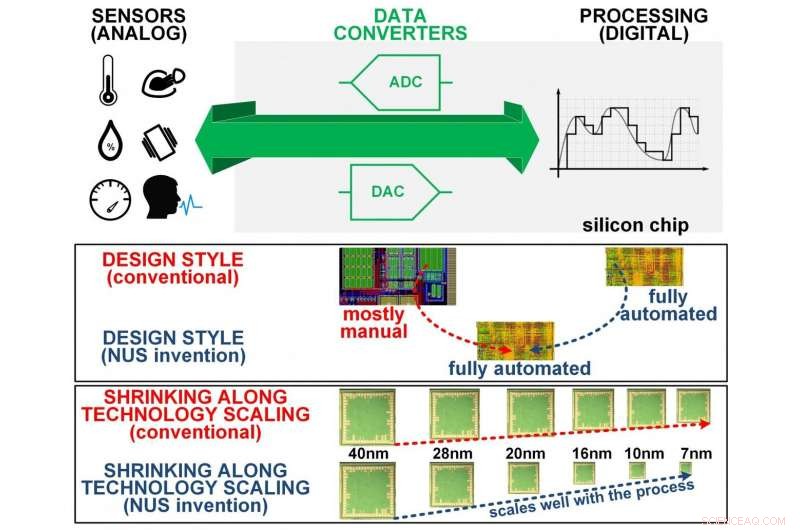

O grupo de pesquisa Green IC do Departamento de Engenharia Elétrica e de Computação da Faculdade de Engenharia da Universidade Nacional de Cingapura (NUS) inventou uma nova classe de Conversores Digital para Analógico (DAC) e Analógico para Digital (ADC) que podem ser totalmente projetado com uma metodologia de design digital totalmente automatizada, graças à sua arquitetura totalmente digital (Fig. 1).

Em comparação com arquiteturas e metodologias analógicas tradicionais, o tempo de resposta do projeto para essas novas interfaces de sensor é reduzido de meses para horas. A redução drástica no esforço de design é altamente benéfica em sistemas de silício sensíveis ao custo, como sensores para a Internet das Coisas (IoT). A nova arquitetura do conversor de dados também tem complexidade muito baixa, reduzindo a área de silício e, portanto, o custo de fabricação em pelo menos 30 vezes, em comparação com designs convencionais.

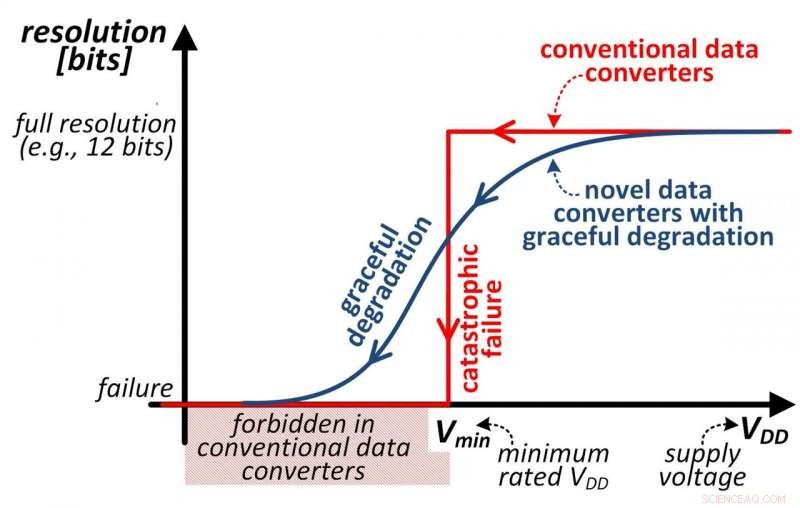

Esses novos conversores de dados também exibem a capacidade sem precedentes de degradar graciosamente a fidelidade do sinal quando a tensão de alimentação ou a frequência do relógio sofrem grandes flutuações (Fig. 2). Essas flutuações são comuns em sensores IoT com captação de energia, sendo que a energia colhida do ambiente circundante (por exemplo, célula solar) é altamente errática. Por sua vez, isso permite o monitoramento ininterrupto do sinal do sensor, mesmo sob condições desfavoráveis de colheita de energia, e sem regulação de tensão. Em vez de, os conversores de dados tradicionais sofrem degradação catastrófica da resolução quando a tensão de alimentação está abaixo de seu valor nominal mínimo Vmin (ou a frequência excede seu valor nominal máximo) como na Fig. 2, portanto, precisando de circuitos que consomem muita energia para regulação de tensão e frequência.

A pesquisa foi conduzida em colaboração com o Professor Associado Paolo Crovetti do Politecnico di Torino, na Itália, e é apoiado pelo Ministério da Educação de Cingapura e pela Comissão da UE.

Interfaces de sensor menores, mais simples e rápido de projetar

"Nossa pesquisa transforma o projeto tradicionalmente analógico e principalmente manual de conversores de dados em um projeto digital totalmente automatizado, reduzindo a área de silício em uma ordem de magnitude e o tempo de design em duas ordens de magnitude, permitindo que as empresas de semicondutores sejam competitivas em termos de custos e, ao mesmo tempo, alcancem os mercados mais rapidamente, "disse o líder da equipe Professor Associado Massimo Alioto, que é do Departamento de Engenharia Elétrica e de Computação da Faculdade de Engenharia da NUS.

A falha catastrófica é substituída pela degradação da resolução elegante na nova classe de conversores de dados convencionais inventados pela equipe da NUS. Isso permite simplificar drasticamente o design do sistema, suprimindo a necessidade de regulação precisa de tensão. Crédito:Universidade Nacional de Cingapura

Ele adicionou, "Ser digital, nossas interfaces de sensor são transportadas sem esforço para tecnologias e aplicações de manufatura, e podem ser imersos em circuitos digitais para evitar o esforço tradicional exigido por sua integração no mesmo chip de silício. ”(Fig. 1).

A equipe da NUS demonstrou o conceito por meio de vários chips de silício implementando DACs e ADCs com área extremamente baixa. Como um exemplo, um DAC de 12 bits fabricado em tecnologia CMOS padrão de 40 nm foi demonstrado com uma área igual ao diâmetro de um fio de cabelo humano. Sua facilidade inerente para escalonamento de tecnologia o faz encolher em aproximadamente outras 32 vezes quando implementado na tecnologia mais avançada atualmente (7 nm).

Ao mesmo tempo, a invenção NUS demonstrou permitir conversores de dados com alta resolução (até 16 bits), ao mesmo tempo em que obtém simplicidade e compactação de design.

Membro da equipe Dr. Orazio Aiello, que é pesquisador visitante no Departamento, disse, "Nossa equipe introduziu um novo paradigma de design que nos empurra para mais perto da visão definitiva de economia, dispositivos IoT ultracompactos e escalonáveis com tecnologia. "

Robustez sem precedentes traz benefícios adicionais ao nível do sistema

A inovação NUS simplifica ainda mais o design do sistema integrado, aproveitando a capacidade sem precedentes de suportar flutuações de tensão e frequência muito substanciais, relaxando assim os requisitos de precisão na geração de tensão e frequência.

A falha catastrófica é substituída pela degradação da resolução elegante na nova classe de conversores de dados convencionais inventados pelos pesquisadores do NUS. Crédito:Universidade Nacional de Cingapura

De fato, conversores de dados convencionais operando em uma tensão de alimentação abaixo de seu valor nominal mínimo (ou frequência de clock excessiva) experimentam falha catastrófica, e, portanto, não consegue realizar sua função pretendida (Fig. 2). Pelo contrário, os conversores de dados inovadores inventados pela equipe NUS exibem degradação graciosa da resolução e fidelidade do sinal quando a tensão de alimentação ou frequência de clock excede sua faixa permitida. Como um exemplo, um DAC projetado para 1 V demonstrou operar corretamente na metade desta tensão, ao mesmo tempo, degradando sua resolução em apenas 1 bit quando a tensão de alimentação é reduzida em 0,3 V substanciais.

Assoc Prof Alioto disse, "A capacidade de ter uma degradação de resolução harmoniosa sob tensão e sobredimensionamento de frequência suprime a necessidade de soluções de circuito complexas que regulem com precisão a tensão de alimentação e a frequência do relógio que está sendo utilizada pelos conversores de dados. Em outras palavras, nossos conversores de dados são mais simples de projetar, e também simplificar o sistema no qual eles são empregados. "

Próximos passos

A equipe está atualmente trabalhando em um novo paradigma que transforma subsistemas de silício tradicionalmente analógicos e de design intensivo em designs baseados em células padrão digitais que são suportados por fluxos de design totalmente automatizados, empurrando os limites do design digitalmente assistido clássico. Este estudo de pesquisa envolve vários subsistemas fundamentais, como amplificadores, osciladores, referências de tensão e corrente, e muitos outros.

A equipe de pesquisa visa transformar a maneira como os sistemas integrados são projetados, permitindo ultra-rápido, design ultracompacto e com tecnologia portátil de sistemas inteiros.