A globalização da cadeia de suprimentos de IC induziu vulnerabilidades em vários estágios de produção de IC. Aqui, os estágios das zonas vermelhas não são confiáveis e podem ser explorados por um invasor. Crédito:Rangarajan et al.

Nos últimos anos, ameaças de segurança centradas em hardware surgiram em diferentes estágios da cadeia de suprimentos do circuito integrado (IC). Isso permitiu a proliferação de vários ataques maliciosos, como pirataria de propriedade intelectual (IP), superprodução ilegal de ICs, e inserção de Trojans de hardware.

De todas as defesas existentes contra a pirataria de IP, até agora, apenas o bloqueio lógico oferece proteção efetiva de ponta a ponta. Para enfrentar esses desafios, uma equipe de pesquisa do Laboratório de Nanoeletrônica e Cibersegurança da Universidade de Nova York desenvolveu uma abordagem de camuflagem dinâmica para impedir a engenharia reversa de IP em todos os estágios da cadeia de suprimentos.

“A globalização da cadeia de suprimentos do circuito integrado resultou na terceirização de várias etapas da produção de chips microeletrônicos, "Nikhil Rangarajan, um dos pesquisadores que realizou o estudo, contado TechXplore . "Os chips são normalmente projetados e / ou adquiridos de um país, fabricado em outro, e finalmente testado e empacotado em outro lugar. Esta cadeia mundial abre muitas oportunidades para que os invasores roubem o IP subjacente, entregue-se à superprodução, ou mesmo inserir modificações maliciosas conhecidas como Trojans de hardware. "

De acordo com as estimativas, a indústria de semicondutores perde bilhões de dólares todos os anos devido ao roubo de IP. Para mitigar esse dano, a pesquisa realizada por Rangarajan e seus colegas enfoca especificamente a prevenção do roubo de IP.

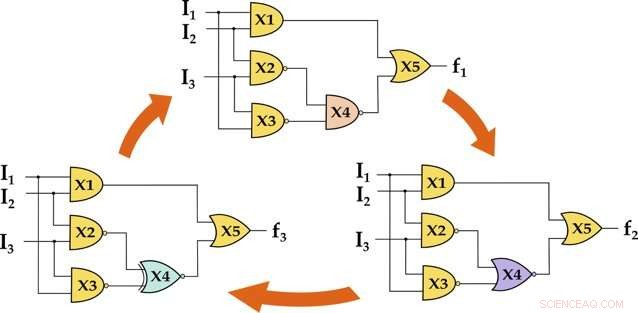

Comutação dinâmica de circuitos polimórficos em tempo real. Crédito:Rangarajan et al.

"A inspiração para a nossa ideia veio da natureza, onde alguns animais como o polvo são capazes de mudar sua aparência física para se adaptar ao seu ambiente para evitar a detecção por presas ou predadores, "Rangarajan explicou." Nós pensamos:por que os circuitos eletrônicos que procuramos proteger não podem mudar dinamicamente para evitar a detecção por um invasor? "

Mecanismos de defesa existentes para a prevenção de roubo de IP, como camuflagem estática, exigem que o projetista confie na fundição comissionada para a fabricação do chip. Pelo contrário, o modelo de ameaça desenvolvido por Rangarajan e seus colegas assume que um invasor também pode residir na fundição ou nas instalações de teste, ou pode ser potencialmente um usuário final.

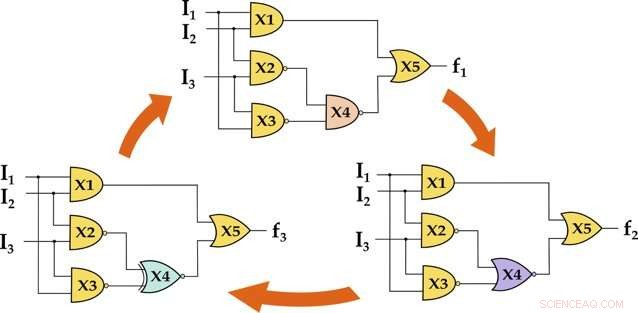

"Usando propriedades inatas como polimorfismo, multifuncionalidade, e reconfigurabilidade pós-fabricação oferecida por dispositivos spintrônicos emergentes, como o dispositivo de órbita magnetoelétrica (MESO), conseguimos uma camuflagem dinâmica, "Satwik Patnaik, outro pesquisador envolvido no estudo, disse TechXplore. "O polimorfismo se destina ao meio específico pelo qual o dispositivo pode implementar prontamente diferentes funções booleanas em tempo de execução, onde a funcionalidade é determinada por um mecanismo de controle interno ou externo. "

No esquema idealizado pelos pesquisadores, uma fundição potencialmente maliciosa fabrica as portas lógicas como "caixas pretas, "que só pode ser configurado pelo projetista quando o processo de fabricação estiver concluído. Isso evita que um invasor dentro da fundição decifre a funcionalidade pretendida do chip que está sendo fabricado, pois ainda não foi configurado.

A camuflagem dinâmica é possível com a ajuda de novas portas spintrônicas como portas MESO. Essas portas podem implementar várias funcionalidades booleanas em um dispositivo e também podem alternar entre elas durante o tempo de execução. Crédito:Rangarajan et al.

"Esta propriedade de 'reconfigurabilidade pós-fabricação' também permite a proteção de instalações de teste não confiáveis, já que o chip pode ser configurado para qualquer funcionalidade fictícia desconhecida para um invasor e restaurado para a verdadeira funcionalidade após o teste ter sido realizado, "Patnaik explicou." Em suma, enquanto trabalhos anteriores em camuflagem de IC são estáticos e precisam confiar na fundição, nosso esquema não exige que o projetista confie na fundição ou nas instalações de teste. "

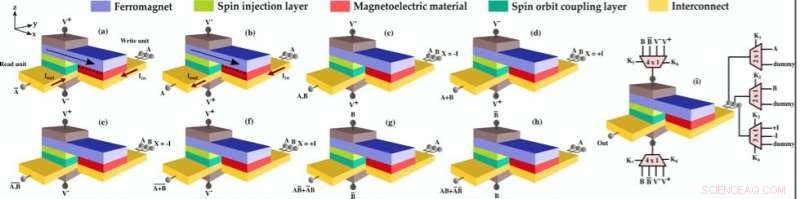

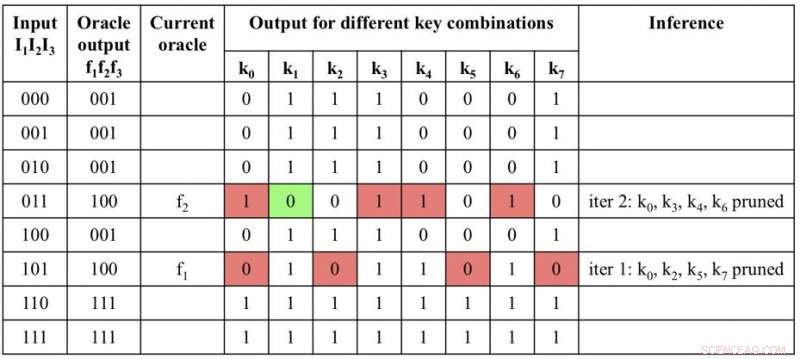

Os pesquisadores avaliaram a eficácia de sua abordagem em neutralizar ataques de mineração de dados de teste de última geração, como HackTest, e análise de canal lateral, onde os adversários visam decifrar a funcionalidade do IP. Eles também exploraram seu desempenho com poderosos ataques de satisfatibilidade booleana, incluindo SAT e SAT aproximado (AppSAT), que são normalmente preferidos pelos usuários finais.

Sua abordagem de camuflagem dinâmica produziu resultados promissores em todos esses testes. No futuro, os pesquisadores acreditam que isso poderia ajudar a impedir os invasores em fundições ou instalações de teste não confiáveis.

"Nosso esquema aproveita as propriedades exclusivas dos dispositivos baseados em spin, "Rangarajan explicou." Essas propriedades, especialmente polimorfismo, não pode ser proporcionado pelas tecnologias CMOS atuais, devido às limitações fundamentais dos dispositivos CMOS. Também queremos enfatizar que a noção geral de camuflagem dinâmica pode ser implementada com outros dispositivos emergentes, contanto que tenham propriedades semelhantes. "

Um ataque de satisfatibilidade booleano montado em um circuito camuflado dinamicamente pode facilmente gerar uma chave incorreta e enganar o invasor. Crédito:Rangarajan et al.

Para promover a implementação de sua técnica de defesa, os pesquisadores também prevêem uma integração híbrida baseada em spin CMOS. Esta integração pode facilitar a adoção e aceitação de seu esquema, bem como de dispositivos que o suportam. De acordo com os pesquisadores, vários estudos acadêmicos estão atualmente caminhando em direções semelhantes.

Rangarajan e seus colegas estão agora planejando investigar as implicações do uso de polimorfismo de tempo de execução para proteger circuitos lógicos aproximados, que têm ganhado muita força nos últimos anos. Esses tipos de circuitos trocam a precisão de saída por uma redução acentuada na dissipação de energia.

"Especialmente com o advento da Internet das Coisas (IoT), acreditamos que a proteção de chips de computação aproximados também é essencial, dado o fato de que eles são amplamente favorecidos para serem usados em sistemas que requerem operação de baixa potência, "Rangarajan disse." Também planejamos avaliar a resiliência de nosso esquema em outros cenários de ataque, para ganhar mais confiança em nossa abordagem. "

© 2018 Science X Network