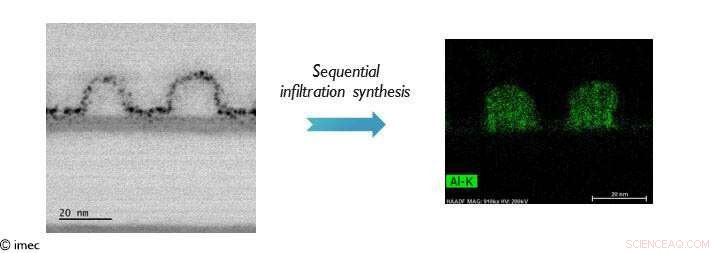

Imagem TEM do padrão fotoresiste após a exposição de litografia (esquerda) e sinal TEM EDX de Alumínio para o padrão fotoresiste após a etapa SIS (direita). Crédito:IMEC

a semana dele, na conferência SPIE Advanced Lithography 2019, imec, um centro de pesquisa e inovação líder mundial em nanoeletrônica e tecnologias digitais, demonstra o impacto positivo da síntese de infiltração sequencial (SIS) no processo de padronização EUVL (litografia ultravioleta extrema). Esta técnica pós-litografia mostra reduzir significativamente as nano-falhas estocásticas e a rugosidade da linha, contribuindo para a introdução de padronização EUVL de nós futuros ". Este trabalho integra avanços recentes em metrologia e etch, e em desenvolvimentos materiais, que será apresentado em vários artigos na Conferência de Litografia Avançada SPIE 2019 desta semana.

SIS é uma técnica existente, usado em automontagem dirigida (DSA) e agora aplicado em litografia EUV, em que o fotorresiste é infiltrado com um elemento inorgânico para torná-lo mais duro e robusto, melhorando assim o desempenho de padronização em parâmetros diferentes. Imec e parceiros mostram a primeira comparação entre um EUVL-SIS e um processo de padronização EUVL padrão, demonstrando os benefícios do SIS em relação à rugosidade, mitigação de nano-falha e variabilidade local. Ao adicionar uma etapa SIS durante uma transferência de padrão completa em uma camada TiN, A imec observou uma melhoria de 60 por cento para uniformidade de dimensão crítica local intra-campo (LCDU) e 10 por cento para rugosidade da borda da linha em comparação com um processo de referência. Esses aprimoramentos de padronização são propriedades inerentes do SIS. Também, o número de nanobreaks - uma nano-falha estocástica típica - é reduzido em pelo menos uma ordem de magnitude. Os resultados foram confirmados em um caso de uso industrial relevante, mostrando defeito reduzido em um chip lógico com uma dimensão crítica ponta a ponta 20 por cento menor em um LCDU semelhante a um processo EUVL padrão.

A melhoria que o SIS apresenta em todos os parâmetros deve-se à infraestrutura de litografia e metrologia EUV da imec e aos avanços recentes no campo do controle de processos, pesquisa de material e etch. O trabalho atual reúne esses resultados e competências em um único artigo, estabelecer o SIS como uma técnica significativa de aprimoramento de padrões de EUV. O progresso em cada um dos aspectos integrados e SIS será apresentado na conferência de Litografia Avançada SPIE em vários artigos.

O trabalho foi realizado em colaboração com ASM e ASML.

"As conquistas recentes com SIS para litografia EUV foram possibilitadas pelo progresso que o imec e seus parceiros fizeram em vários domínios, como ciência dos materiais, deposição, imagem, e metrologia. Este é um ótimo exemplo de como a integração de conhecimento e esforços combinados de vários domínios e parceiros do ecossistema permitirá um caminho para escalar para N3 e além, "disse Greg McIntyre, diretor de padronização avançada do imec.