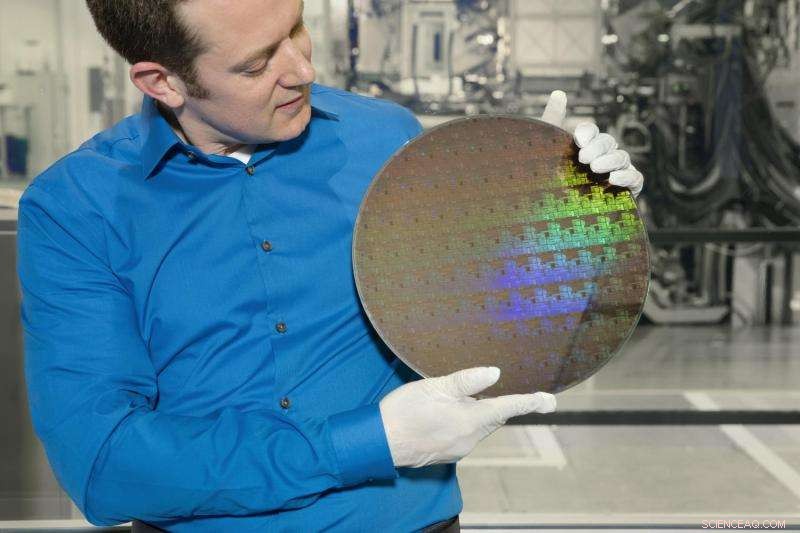

O cientista da IBM Research, Nicolas Loubet, possui uma pastilha de chips com transistores de nanofolha de silício de 5 nm fabricados usando um processo pioneiro do setor que pode fornecer 40 por cento de melhoria de desempenho em potência fixa, ou 75 por cento de economia de energia com desempenho compatível. Crédito:Connie Zhou

IBM, seus parceiros da Research Alliance Globalfoundries e Samsung, e os fornecedores de equipamentos desenvolveram um processo pioneiro na indústria para construir transistores de nanofolha de silício que habilitará chips de 5 nanômetros (nm). Os detalhes do processo serão apresentados nos Simpósios de Tecnologia e Circuitos VLSI 2017 em Kyoto, Japão. Em menos de dois anos, desde o desenvolvimento de um chip de nó de teste de 7 nm com 20 bilhões de transistores, os cientistas abriram caminho para 30 bilhões de interruptores em um chip do tamanho de uma unha.

O aumento resultante no desempenho ajudará a acelerar a computação cognitiva, a Internet das Coisas (IoT), e outros aplicativos com uso intensivo de dados fornecidos na nuvem. A economia de energia também pode significar que as baterias em smartphones e outros produtos móveis podem durar duas a três vezes mais do que os dispositivos de hoje, antes de precisar ser cobrado.

Cientistas que trabalham como parte da Aliança de Pesquisa liderada pela IBM no SUNY Polytechnic Institute Colleges of Nanoscale Science and Engineering's NanoTech Complex em Albany, NY conseguiu a descoberta usando pilhas de nanofolhas de silício como a estrutura do dispositivo do transistor, em vez da arquitetura FinFET padrão, que é o projeto para a indústria de semicondutores até a tecnologia de nó de 7 nm.

"Para que as empresas e a sociedade atendam às demandas de computação cognitiva e em nuvem nos próximos anos, o avanço na tecnologia de semicondutores é essencial, "disse Arvind Krishna, vice presidente Senior, Nuvem Híbrida, e diretor, IBM Research. "É por isso que a IBM busca agressivamente novas e diferentes arquiteturas e materiais que ultrapassam os limites desta indústria, e os traz ao mercado em tecnologias como mainframes e nossos sistemas cognitivos. "

Cientistas da IBM no SUNY Polytechnic Institute Colleges of Nanoscale Science and Engineering's NanoTech Complex em Albany, NY prepara wafers de teste com transistores de nanofolha de silício de 5 nm, carregado no pod unificado de abertura frontal, ou FOUPs, para testar um processo pioneiro da indústria de construção de transistores de 5 nm usando nanofolhas de silício. Crédito:Connie Zhou

A demonstração do transistor de nanofolha de silício, conforme detalhado no documento da Research Alliance Stacked Nanosheet Gate-All-Around Transistor para habilitar o dimensionamento além do FinFET, e publicado pela VLSI, prova que chips de 5 nm são possíveis, mais poderoso, e não muito longe no futuro.

Em comparação com a tecnologia de ponta de 10 nm disponível no mercado, uma tecnologia de 5 nm baseada em nanosheet pode fornecer 40 por cento de melhoria de desempenho em potência fixa, ou 75 por cento de economia de energia com desempenho compatível. Esta melhoria permite um impulso significativo para atender às demandas futuras de sistemas de inteligência artificial (IA), realidade virtual e dispositivos móveis.

Construindo um Novo Switch

"Este anúncio é o exemplo mais recente de pesquisa de classe mundial que continua a emergir de nossa parceria público-privada inovadora em Nova York, "disse Gary Patton, CTO e chefe de P&D mundial da Globalfoundries. "À medida que avançamos na comercialização de 7 nm em 2018 em nossa fábrica da Fab 8, estamos buscando ativamente tecnologias de próxima geração a 5 nm e além para manter a liderança em tecnologia e permitir que nossos clientes produzam um menor, mais rápido, e geração de semicondutores com melhor custo-benefício. "

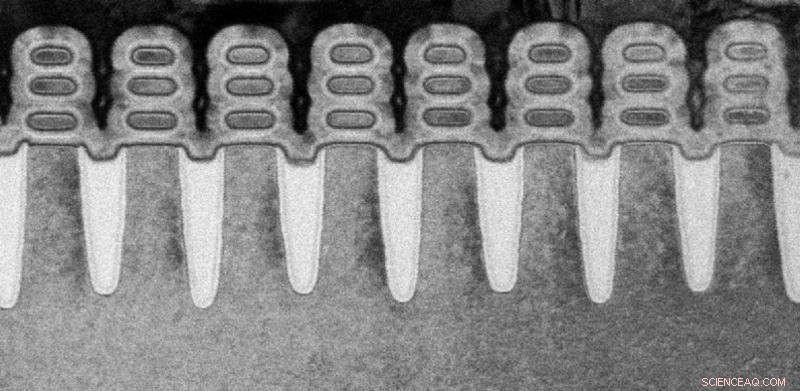

Na foto:uma varredura do transistor de 5 nm da IBM Research Alliance, construído usando um processo pioneiro da indústria para empilhar nanofolhas de silício como a estrutura do dispositivo - alcançando uma escala de 30 bilhões de switches em um chip do tamanho de uma unha que fornecerá melhorias significativas de potência e desempenho em relação aos chips de 10 nm de última geração. Crédito:IBM

A IBM Research explorou a tecnologia de semicondutores de nanofolhas por mais de 10 anos. Este trabalho é o primeiro na indústria a demonstrar a viabilidade de projetar e fabricar dispositivos de nanofolhas empilhadas com propriedades elétricas superiores à arquitetura FinFET.

Esta mesma abordagem de litografia ultravioleta extrema (EUV) usada para produzir o nó de teste de 7 nm e seus 20 bilhões de transistores foi aplicada à arquitetura de transistor de nanofolha. Usando litografia EUV, a largura das nanofolhas pode ser ajustada continuamente, tudo dentro de um único processo de fabricação ou design de chip. Esta capacidade de ajuste permite o ajuste fino de desempenho e potência para circuitos específicos - algo que não é possível com a produção de arquitetura de transistor FinFET de hoje, que é limitado pela altura da barbatana que carrega a corrente. Portanto, enquanto os chips FinFET podem escalar até 5 nm, simplesmente reduzir a quantidade de espaço entre as aletas não fornece fluxo de corrente aumentado para desempenho adicional.

"O anúncio de hoje continua a colaboração do modelo público-privado com a IBM que está energizando a SUNY-Polytechnic's, Albany, e a liderança e inovação do estado de Nova York no desenvolvimento de tecnologias de próxima geração, "disse o Dr. Bahgat Sammakia, Presidente interino, SUNY Polytechnic Institute. "Acreditamos que habilitar o primeiro transistor de 5 nm é um marco significativo para toda a indústria de semicondutores, à medida que continuamos a ultrapassar as limitações de nossas capacidades atuais. A parceria da SUNY Poly com a IBM e a Empire State Development é um exemplo perfeito de como a indústria, O governo e a academia podem colaborar com sucesso e ter um impacto amplo e positivo na sociedade. "

Parte dos US $ 3 bilhões da IBM, investimento de cinco anos em P&D de chips (anunciado em 2014), a prova do dimensionamento da arquitetura de nanosheet para um nó de 5 nm continua o legado de contribuições históricas da IBM para a inovação em silício e semicondutores. Eles incluem a invenção ou a primeira implementação da DRAM de célula única, as Leis de Escala de Dennard, fotoresiste amplificado quimicamente, fiação de interconexão de cobre, Silício no isolador, engenharia exigente, microprocessadores multi-core, litografia de imersão, SiGe de alta velocidade, Dielétricos de porta de alto k, DRAM embutido, Empilhamento de chips 3-D e isoladores de entreferro.