p O estresse mecânico de tração pode ter um efeito útil para alguns transistores, onde a deformação atômica resultante permite aos seus pares de elétron-buraco portadores de corrente melhor mobilidade. Contudo, quando esse estresse é aplicado a todo o dispositivo, como é uma abordagem popular por meio do uso do que é chamado de camadas de parada de gravação de contato (CESLs), a região de deriva adjacente ao canal esticado é comprimida e resulta em desempenho reduzido. p Uma equipe de pesquisa na China desenvolveu um novo método CESL que introduz tensão de tração tanto no canal quanto na região de deriva, melhorando o desempenho geral, oferecendo baixa resistência à deriva, alta frequência de corte e características de quebra desejáveis. Seu trabalho é descrito em um artigo publicado esta semana na revista.

AIP Advances .

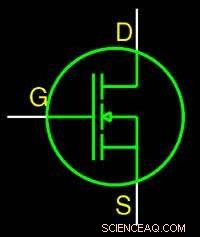

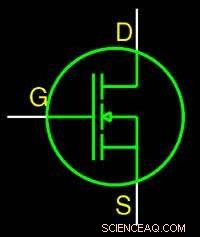

p A equipe de pesquisadores se interessou pelo método devido ao trabalho realizado em técnicas de silício filtrado. Durante a pesquisa sobre transistores de efeito de campo semicondutores de meta-óxido deformados (MOSFETs), os pesquisadores viram que a tensão na região da fonte / dreno era inversa à tensão na região do canal. Com base nessas observações, eles começaram a estudar como poderiam usar esse fenômeno de uma forma que pudesse melhorar o desempenho.

p Esta nova pesquisa se concentrou em dispositivos parciais de silício sobre isolante (PSOI) que introduzem tensão de tração tanto no canal quanto na região de deriva usando os CESLs. Os resultados da simulação também mostraram que o dispositivo PSOI oferece melhor desempenho de frequência e capacidade de condução do que dispositivos sem restrições.

p "O mais difícil para nós foi encontrar um custo baixo, Método compatível com CMOS para aplicação de estresse mecânico, "disse Xiangzhan Wang, da Universidade de Ciência Eletrônica e Tecnologia da China. “Durante o processo de fabricação, o wafer se dobra conforme o filme de estresse (Si3N4) cresce, o que cria um problema em segurar o wafer no equipamento de processo. "

p Os resultados do experimento, Contudo, maior confiança de que a nova técnica de tensão não poderia ser aplicada apenas a pequenos dispositivos, mas também para dispositivos bastante grandes para produzir melhoria de desempenho. Com os resultados, até mesmo a equipe de pesquisa ficou surpresa com o nível de melhoria que proporcionou às suas simulações.

p "Em nossa simulação, o LDMOSFET PSOI tipo n totalmente tensionado por tração mostrou uma melhoria de corrente de 20-30 por cento conduzindo em relação ao LDMOSFET de Si normal, "Disse Wang." Mas quando usamos este método de cepa com um produto comercial Si LDMOS, a corrente motriz dobrou, resultando em um aumento de corrente de mais de 100 por cento, o que foi bastante surpreendente para nós. "

p Embora este trabalho tenha contribuído para a compreensão dos mecanismos de Si tensos, ainda há mais para melhorar e entender.

p "As próximas orientações de pesquisa para a equipe são otimizar o processo de fabricação desses dispositivos, a fim de obter melhor estabilidade e tentar aplicar o mesmo método a um dispositivo não simétrico, como um túnel FET, "Disse Wang.

p O estresse mecânico de tração pode ter um efeito útil para alguns transistores, onde a deformação atômica resultante permite aos seus pares de elétron-buraco portadores de corrente melhor mobilidade. Contudo, quando esse estresse é aplicado a todo o dispositivo, como é uma abordagem popular por meio do uso do que é chamado de camadas de parada de gravação de contato (CESLs), a região de deriva adjacente ao canal esticado é comprimida e resulta em desempenho reduzido. p Uma equipe de pesquisa na China desenvolveu um novo método CESL que introduz tensão de tração tanto no canal quanto na região de deriva, melhorando o desempenho geral, oferecendo baixa resistência à deriva, alta frequência de corte e características de quebra desejáveis. Seu trabalho é descrito em um artigo publicado esta semana na revista. AIP Advances .

p A equipe de pesquisadores se interessou pelo método devido ao trabalho realizado em técnicas de silício filtrado. Durante a pesquisa sobre transistores de efeito de campo semicondutores de meta-óxido deformados (MOSFETs), os pesquisadores viram que a tensão na região da fonte / dreno era inversa à tensão na região do canal. Com base nessas observações, eles começaram a estudar como poderiam usar esse fenômeno de uma forma que pudesse melhorar o desempenho.

p Esta nova pesquisa se concentrou em dispositivos parciais de silício sobre isolante (PSOI) que introduzem tensão de tração tanto no canal quanto na região de deriva usando os CESLs. Os resultados da simulação também mostraram que o dispositivo PSOI oferece melhor desempenho de frequência e capacidade de condução do que dispositivos sem restrições.

p "O mais difícil para nós foi encontrar um custo baixo, Método compatível com CMOS para aplicação de estresse mecânico, "disse Xiangzhan Wang, da Universidade de Ciência Eletrônica e Tecnologia da China. “Durante o processo de fabricação, o wafer se dobra conforme o filme de estresse (Si3N4) cresce, o que cria um problema em segurar o wafer no equipamento de processo. "

p Os resultados do experimento, Contudo, maior confiança de que a nova técnica de tensão não poderia ser aplicada apenas a pequenos dispositivos, mas também para dispositivos bastante grandes para produzir melhoria de desempenho. Com os resultados, até mesmo a equipe de pesquisa ficou surpresa com o nível de melhoria que proporcionou às suas simulações.

p "Em nossa simulação, o LDMOSFET PSOI tipo n totalmente tensionado por tração mostrou uma melhoria de corrente de 20-30 por cento conduzindo em relação ao LDMOSFET de Si normal, "Disse Wang." Mas quando usamos este método de cepa com um produto comercial Si LDMOS, a corrente motriz dobrou, resultando em um aumento de corrente de mais de 100 por cento, o que foi bastante surpreendente para nós. "

p Embora este trabalho tenha contribuído para a compreensão dos mecanismos de Si tensos, ainda há mais para melhorar e entender.

p "As próximas orientações de pesquisa para a equipe são otimizar o processo de fabricação desses dispositivos, a fim de obter melhor estabilidade e tentar aplicar o mesmo método a um dispositivo não simétrico, como um túnel FET, "Disse Wang.

p O estresse mecânico de tração pode ter um efeito útil para alguns transistores, onde a deformação atômica resultante permite aos seus pares de elétron-buraco portadores de corrente melhor mobilidade. Contudo, quando esse estresse é aplicado a todo o dispositivo, como é uma abordagem popular por meio do uso do que é chamado de camadas de parada de gravação de contato (CESLs), a região de deriva adjacente ao canal esticado é comprimida e resulta em desempenho reduzido. p Uma equipe de pesquisa na China desenvolveu um novo método CESL que introduz tensão de tração tanto no canal quanto na região de deriva, melhorando o desempenho geral, oferecendo baixa resistência à deriva, alta frequência de corte e características de quebra desejáveis. Seu trabalho é descrito em um artigo publicado esta semana na revista. AIP Advances .

p A equipe de pesquisadores se interessou pelo método devido ao trabalho realizado em técnicas de silício filtrado. Durante a pesquisa sobre transistores de efeito de campo semicondutores de meta-óxido deformados (MOSFETs), os pesquisadores viram que a tensão na região da fonte / dreno era inversa à tensão na região do canal. Com base nessas observações, eles começaram a estudar como poderiam usar esse fenômeno de uma forma que pudesse melhorar o desempenho.

p Esta nova pesquisa se concentrou em dispositivos parciais de silício sobre isolante (PSOI) que introduzem tensão de tração tanto no canal quanto na região de deriva usando os CESLs. Os resultados da simulação também mostraram que o dispositivo PSOI oferece melhor desempenho de frequência e capacidade de condução do que dispositivos sem restrições.

p "O mais difícil para nós foi encontrar um custo baixo, Método compatível com CMOS para aplicação de estresse mecânico, "disse Xiangzhan Wang, da Universidade de Ciência Eletrônica e Tecnologia da China. “Durante o processo de fabricação, o wafer se dobra conforme o filme de estresse (Si3N4) cresce, o que cria um problema em segurar o wafer no equipamento de processo. "

p Os resultados do experimento, Contudo, maior confiança de que a nova técnica de tensão não poderia ser aplicada apenas a pequenos dispositivos, mas também para dispositivos bastante grandes para produzir melhoria de desempenho. Com os resultados, até mesmo a equipe de pesquisa ficou surpresa com o nível de melhoria que proporcionou às suas simulações.

p "Em nossa simulação, o LDMOSFET PSOI tipo n totalmente tensionado por tração mostrou uma melhoria de corrente de 20-30 por cento conduzindo em relação ao LDMOSFET de Si normal, "Disse Wang." Mas quando usamos este método de cepa com um produto comercial Si LDMOS, a corrente motriz dobrou, resultando em um aumento de corrente de mais de 100 por cento, o que foi bastante surpreendente para nós. "

p Embora este trabalho tenha contribuído para a compreensão dos mecanismos de Si tensos, ainda há mais para melhorar e entender.

p "As próximas orientações de pesquisa para a equipe são otimizar o processo de fabricação desses dispositivos, a fim de obter melhor estabilidade e tentar aplicar o mesmo método a um dispositivo não simétrico, como um túnel FET, "Disse Wang.