Pesquisadores avançam esquema para projetar circuitos integrados contínuos gravados em grafeno

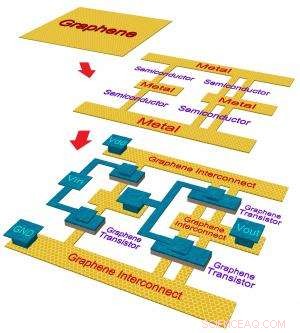

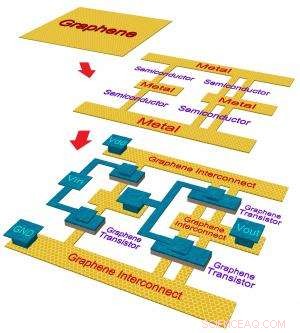

p O esquema superior é uma folha de grafeno monocamada. O esquema central exibe fitas estreitas / largas gravadas agindo como semicondutor / metal. O esquema inferior é um circuito todo de grafeno após a deposição e padronização de metal e dielétrico de porta. Crédito:UCSB Nanoelectronics Research Lab

p O esquema superior é uma folha de grafeno monocamada. O esquema central exibe fitas estreitas / largas gravadas agindo como semicondutor / metal. O esquema inferior é um circuito todo de grafeno após a deposição e padronização de metal e dielétrico de porta. Crédito:UCSB Nanoelectronics Research Lab

p (Phys.org) - Pesquisadores em engenharia elétrica e de computação na Universidade da Califórnia, Santa Bárbara introduziu e modelou um esquema de design de circuito integrado no qual os transistores e as interconexões são padronizados monoliticamente e perfeitamente em uma folha de grafeno, um plano bidimensional de átomos de carbono. A demonstração oferece possibilidades de ultra-eficiência energética, flexível, e eletrônicos transparentes. p Os materiais a granel comumente usados para fazer transitores CMOS e interconexões representam desafios fundamentais na redução contínua de seus tamanhos de recursos e sofrem com o aumento da "resistência de contato" entre eles, ambos levam à degradação do desempenho e ao aumento do consumo de energia. Transistores e interconexões baseados em grafeno são uma tecnologia promissora em nanoescala que pode potencialmente resolver os problemas de transistores tradicionais baseados em silício e interconexões de metal.

p "Além de suas superfícies atomicamente finas e imaculadas, o grafeno tem uma lacuna de banda ajustável, que pode ser ajustado por esboços litográficos de padrões - fitas estreitas de grafeno podem ser feitas semicondutoras enquanto fitas mais largas são metálicas. Portanto, fitas de grafeno contíguas podem ser previstas a partir do mesmo material de partida para projetar dispositivos ativos e passivos de uma forma contínua e resistências de interface / contato mais baixas, "explicou Kaustav Banerjee, professor de engenharia elétrica e da computação e diretor do Laboratório de Pesquisa em Nanoeletrônica da UCSB. A equipe de pesquisa de Banerjee também inclui os pesquisadores da UCSB Jiahao Kang, Deblina Sarkar e Yasin Khatami. Seu trabalho foi publicado recentemente na revista

Cartas de Física Aplicada .

p "A avaliação precisa do transporte elétrico por meio de vários dispositivos baseados em nanofita de grafeno e interconexões e através de suas interfaces foi a chave para o nosso projeto e otimização de circuito bem-sucedidos, "explicou Jiahao Kang, um aluno de doutorado no grupo de Banerjee e um co-autor do estudo. O grupo de Banerjee foi pioneiro em uma metodologia usando a técnica da Função de Green Non-Equilibrium (NEGF) para avaliar o desempenho de tais esquemas de circuitos complexos envolvendo muitas heterojunções. Esta metodologia foi usada no projeto de um circuito lógico "totalmente em grafeno" relatado neste estudo.

p "Este trabalho demonstrou uma solução para o sério problema de resistência de contato encontrado na tecnologia de semicondutor convencional, fornecendo uma ideia inovadora de usar um esquema de interconexão de dispositivo totalmente de grafeno. Isso simplificará significativamente o processo de fabricação de IC de dispositivos nanoeletrônicos baseados em grafeno." comentou Philip Kim, professor de física na Columbia University, e um renomado cientista no mundo do grafeno.

p Conforme relatado em seu estudo, os circuitos propostos totalmente de grafeno alcançaram margens de ruído 1.7X maiores e consumo de energia estática de 1-2 décadas menor em relação à tecnologia CMOS atual. De acordo com Banerjee, com os esforços mundiais em curso na padronização e dopagem do grafeno, tais circuitos podem ser realizados em um futuro próximo.

p "Esperamos que este trabalho incentive e inspire outros pesquisadores a explorar o grafeno e além do grafeno emergentes cristais bidimensionais para projetar tais circuitos de 'engenharia de folga de banda' em um futuro próximo, "adicionou Banerjee.