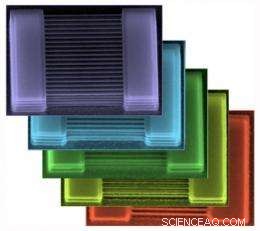

Cinco estruturas de teste diferentes apresentam pilhas de nanofios com diferentes números de níveis. A estrutura inferior possui apenas um nível; a estrutura superior possui cinco. Imagens:Judy Hoyt, Pouya Hashemi e Leonardo Gomez

(PhysOrg.com) - Os computadores ficam cada vez mais poderosos porque os transistores de silício ficam cada vez menores. Mas essa miniaturização não pode continuar muito mais longe sem uma mudança no design dos transistores, que permaneceu mais ou menos o mesmo por 40 anos.

Um sucessor potencial para os transistores de silício de hoje são os nanofios de silício, minúsculos filamentos de silício suspensos como cordas de um violão entre almofadas condutoras de eletricidade. Mas embora os nanofios de silício sejam certamente pequenos o suficiente para manter a miniaturização dos circuitos do computador nos trilhos, há dúvidas sobre se eles podem passar corrente elétrica suficiente para a computação de alta velocidade. No Encontro Internacional de Dispositivos Eletrônicos de 2008, pesquisadores do Laboratório de Tecnologia de Microsistemas do MIT demonstraram nanofios de silício com o dobro da mobilidade de elétrons - o que indica a facilidade com que a corrente pode ser induzida - de seus antecessores. Agora, o mesmo grupo mostrou que pode construir chips nos quais até cinco nanofios de alto desempenho são empilhados uns sobre os outros. Isso permitiria que os transistores de nanofios passassem até cinco vezes mais corrente sem ocupar mais área na superfície do chip, um passo crucial para estabelecer a viabilidade dos transistores de nanofios de silício.

Um transistor é basicamente um interruptor:quando está ligado, passa uma corrente elétrica, e quando está desligado, isso não acontece. Girar a chave requer o carregamento de uma parte do transistor chamada de "portão". No design de hoje, o portão fica em cima do transistor. Mas se o transistor ficar pequeno o suficiente, eletricidade vazará através dele, esteja o portão carregado ou não. Desligar o interruptor torna-se impossível.

Como os nanofios de silício estão suspensos no ar, o portão pode ser enrolado em volta deles, como isolamento em torno de um fio elétrico, o que melhora o controle do switch. Mas a estreiteza dos nanofios limita a quantidade de corrente que eles podem passar.

A professora de engenharia elétrica Judy Hoyt e seus alunos de graduação Pouya Hashemi e Leonardo Gomez melhoraram o desempenho dos transistores de nanofios de silício por, basicamente, separando os átomos de silício ligeiramente mais distantes do que estariam naturalmente, o que permite que os elétrons fluam através dos fios mais livremente. Esse “silício tensionado” tem sido uma forma padrão de melhorar o desempenho dos transistores convencionais desde 2003. Mas Hoyt foi um dos primeiros pesquisadores na área.

“A partir do início dos anos 1990, ela realmente desempenhou um papel pioneiro na tecnologia de silício deformado, ”Diz Tahir Ghani, diretor de tecnologia de transistor e integração do Grupo de Tecnologia e Fabricação da Intel. “Ela fez muito desse trabalho pioneiro que, pela primeira vez, demonstrou que você pode ter ganhos de desempenho significativos implementando deformação na tecnologia de silício.” Hoyt e o trabalho de seu grupo em nanofios de silício tenso, Ghani diz, “Combina os dois elementos principais dos transistores” - desempenho e eficiência de espaço - “ambos são essenciais para o dimensionamento no futuro. E assim, desse ponto de vista, isso o torna muito relevante para a indústria ”.

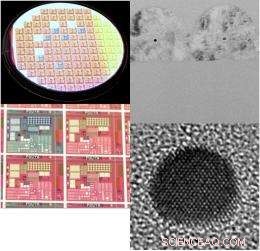

Quatro ampliações sucessivas de um chip de teste com circuitos de nanofios. (1) Um wafer com dezenas de chips gravados nele. (2) Um close-up de quatro chips. (3) Seções transversais de dois nanofios em um transistor:nos centros estão os nanofios; ao redor deles estão os elementos de transistor chamados de "portas". (4) Um close-up do fio. Imagens:Judy Hoyt, Pouya Hashemi e Leonardo Gomez

Lidando com o estresse

Para construir seus transistores de nanofios empilhados, os pesquisadores do MIT começam com uma pastilha de silício normal, no qual eles depositam um composto de silício-germânio. Como os átomos de germânio são maiores do que os átomos de silício, as distâncias entre os átomos na camada de silício-germânio são maiores do que seriam em uma camada de silício puro. Quando os pesquisadores depositam outra camada de silício no topo do compósito, os átomos de silício tentam se alinhar com os átomos abaixo deles, então eles, também, acabam espaçadas ligeiramente mais afastadas.

Esta camada de silício tensionada é ligada a uma segunda pastilha de silício, e as outras camadas são removidas, deixando o segundo wafer coberto com uma camada de base de silício filtrado. Os pesquisadores então empilham camadas alternadas de silício-germânio e silício no topo da camada de base, passando sua deformação para cada camada sucessiva de silício. Usando uma técnica chamada litografia de feixe de elétrons, os pesquisadores padronizam linhas finas nas pilhas e então marcam o material entre as linhas. Finalmente, eles gravam o silício-germânio restante, e eles ficam com várias camadas de nanofios de silício suspensos. Hoyt e seus alunos fabricaram nanofios com diâmetro de apenas oito nanômetros, que eles descreveram em um artigo de 2009 no periódico Electron Device Letters do Institute of Electrical and Electronics Engineers; por contraste, os menores elementos dos chips de computador atuais têm 45 nanômetros de diâmetro.

Hoyt diz que seu grupo pode criar silício com o dobro da tensão observada em chips fabricados por fornecedores comerciais. “Aumentamos a fração de germânio da camada inicial, portanto, criamos mais estresse no silício, ”Hoyt diz. Além disso, diz Hashemi, “Somos o único grupo no mundo que mostrou que podemos manter esta tensão após a suspensão” - isto é, uma vez que as camadas subjacentes foram cortadas.

Até aqui, O grupo de Hoyt construiu transistores de nanofios nos quais a carga é transportada por elétrons em movimento. Mas para maximizar a eficiência computacional, um chip de computador padrão usa, na verdade, dois tipos de transistores. No outro tipo, a carga é transportada pelos chamados orifícios. Um buraco é simplesmente a ausência de um elétron em um cristal de material semicondutor. Quando um elétron desliza para preencher o buraco, ele desocupa seu próprio lugar no cristal; outro elétron desliza para preencher aquele ponto; e assim por diante. Desta maneira, o buraco na verdade se move ao longo do comprimento do cristal.

Aumentar a mobilidade dos orifícios em tais transistores requer um tipo diferente de tensão:os átomos do cristal realmente precisam estar mais próximos do que seja confortável. Então, o grupo de Hoyt agora está trabalhando para construir nanofios a partir de um composto de silício-germânio, onde camadas intermediárias de silício puro causam compressão em vez de tensão.