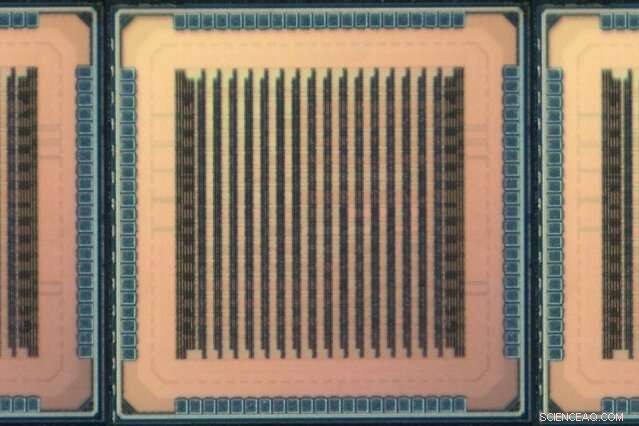

Os pesquisadores do MIT desenvolveram um novo chip que pode computar esquemas complexos de criptografia à prova de quantum com eficiência suficiente para proteger dispositivos de baixa potência da “internet das coisas” (IoT). Crédito:Massachusetts Institute of Technology

Os pesquisadores do MIT desenvolveram um novo circuito de criptografia que pode ser usado para proteger dispositivos de baixa potência da "internet das coisas" (IoT) na era vindoura da computação quântica.

Os computadores quânticos podem, em princípio, executar cálculos que hoje são praticamente impossíveis para os computadores clássicos. Colocar os computadores quânticos online e no mercado pode um dia permitir avanços na pesquisa médica, descoberta de drogas, e outros aplicativos. Mas há um problema:se os hackers também tiverem acesso a computadores quânticos, eles poderiam quebrar os poderosos esquemas de criptografia que atualmente protegem os dados trocados entre os dispositivos.

O esquema de criptografia resistente ao quantum mais promissor de hoje é chamado de "criptografia baseada em rede, "que esconde informações em estruturas matemáticas extremamente complicadas. Até o momento, nenhum algoritmo quântico conhecido pode romper suas defesas. Mas esses esquemas são muito computacionalmente intensos para dispositivos IoT, que só pode poupar energia suficiente para processamento de dados simples.

Em um artigo apresentado na recente Conferência Internacional de Circuitos de Estado Sólido, Os pesquisadores do MIT descrevem uma nova arquitetura de circuito e truques de otimização estatística que podem ser usados para computar com eficiência a criptografia baseada em rede. Os chips de 2 milímetros quadrados que a equipe desenvolveu são eficientes o suficiente para integração em qualquer dispositivo IoT atual.

A arquitetura é personalizável para acomodar os múltiplos esquemas baseados em rede atualmente sendo estudados em preparação para o dia em que os computadores quânticos ficarão online. "Isso pode levar algumas décadas a partir de agora, mas descobrir se essas técnicas são realmente seguras leva muito tempo, "diz o primeiro autor Utsav Banerjee, um estudante de graduação em engenharia elétrica e ciência da computação. "Pode parecer cedo, mas antes é sempre melhor. "

Além disso, os pesquisadores dizem, o circuito é o primeiro de seu tipo a atender aos padrões de criptografia baseada em rede definida pelo Instituto Nacional de Padrões e Tecnologia (NIST), uma agência do Departamento de Comércio dos EUA que encontra e redige regulamentos para os esquemas de criptografia atuais.

Juntando-se a Banerjee no papel estão Anantha Chandrakasan, reitor da Escola de Engenharia do MIT e Professor de Engenharia Elétrica e Ciência da Computação Vannevar Bush, e Abhishek Pathak do Instituto Indiano de Tecnologia.

Amostragem eficiente

Em meados da década de 1990, O professor Peter Shor do MIT desenvolveu um algoritmo quântico que pode essencialmente quebrar todos os esquemas de criptografia modernos. Desde então, O NIST tem tentado encontrar os esquemas de criptografia pós-quântica mais seguros. Isso acontece em fases; cada fase exibe uma lista dos esquemas mais seguros e práticos. Duas semanas atrás, a agência entrou em sua segunda fase de criptografia pós-quântica, com esquemas baseados em rede, constituindo metade de sua lista.

No novo estudo, os pesquisadores primeiro implementaram em microprocessadores comerciais vários esquemas de criptografia baseados em rede NIST desde a primeira fase da agência. Isso revelou dois gargalos de eficiência e desempenho:geração de números aleatórios e armazenamento de dados.

Gerar números aleatórios é a parte mais importante de todos os esquemas de criptografia, porque esses números são usados para gerar chaves de criptografia seguras que não podem ser previstas. Isso é calculado por meio de um processo de duas partes chamado "amostragem".

A amostragem primeiro gera números pseudo-aleatórios de um conhecido, conjunto finito de valores com probabilidade igual de serem selecionados. Então, uma etapa de "pós-processamento" converte esses números pseudo-aleatórios em uma distribuição de probabilidade diferente com um desvio padrão especificado - um limite de quanto os valores podem variar entre si - que torna os números ainda mais aleatórios. Basicamente, os números aleatórios devem satisfazer parâmetros estatísticos cuidadosamente escolhidos. Este difícil problema matemático consome cerca de 80 por cento de toda a energia de computação necessária para a criptografia baseada em rede.

Depois de analisar todos os métodos disponíveis para amostragem, os pesquisadores descobriram que um método, chamado SHA-3, pode gerar muitos números pseudo-aleatórios duas ou três vezes mais eficientemente do que todos os outros. Eles ajustaram o SHA-3 para lidar com a amostragem de criptografia baseada em rede. Além do mais, eles aplicaram alguns truques matemáticos para fazer uma amostragem pseudo-aleatória, e a conversão pós-processamento para novas distribuições, mais rápido e eficiente.

Eles executam essa técnica usando hardware personalizado com eficiência energética que ocupa apenas 9% da área de superfície de seu chip. No fim, isso torna o processo de amostragem de duas ordens de magnitude mais eficiente do que os métodos tradicionais.

Dividindo os dados

No lado do hardware, os pesquisadores fizeram inovações no fluxo de dados. A criptografia baseada em rede processa dados em vetores, que são tabelas com algumas centenas ou milhares de números. Armazenar e mover esses dados requer componentes de memória física que ocupam cerca de 80 por cento da área de hardware de um circuito.

Tradicionalmente, os dados são armazenados em um único dispositivo de memória de acesso aleatório (RAM) de duas ou quatro portas. Dispositivos multiportas permitem a alta taxa de transferência de dados necessária para esquemas de criptografia, mas ocupam muito espaço.

Para o projeto do circuito, os pesquisadores modificaram uma técnica chamada "transformação teórica dos números" (NTT), que funciona de forma semelhante à técnica matemática da transformada de Fourier, que decompõe um sinal nas múltiplas frequências que o compõem. O NTT modificado divide os dados vetoriais e aloca porções em quatro dispositivos RAM de porta única. Cada vetor ainda pode ser acessado em sua totalidade para amostragem, como se estivesse armazenado em um único dispositivo multiporta. O benefício é que quatro dispositivos REM de porta única ocupam cerca de um terço a menos da área total do que um dispositivo multiporta.

"Basicamente, modificamos como o vetor é mapeado fisicamente na memória e modificamos o fluxo de dados, portanto, esse novo mapeamento pode ser incorporado ao processo de amostragem. Usando esses truques de arquitetura, reduzimos o consumo de energia e a área ocupada, enquanto mantém a taxa de transferência desejada, "Banerjee diz.

O circuito também incorpora um pequeno componente de memória de instrução que pode ser programado com instruções personalizadas para lidar com diferentes técnicas de amostragem - como distribuições de probabilidade específicas e desvios padrão - e diferentes tamanhos de vetor e operações. Isso é especialmente útil, já que os esquemas de criptografia baseados em rede provavelmente mudarão um pouco nos próximos anos e décadas.

Parâmetros ajustáveis também podem ser usados para otimizar a eficiência e a segurança. Quanto mais complexo o cálculo, quanto menor a eficiência, e vice versa. Em seu jornal, os pesquisadores detalham como navegar nessas compensações com seus parâmetros ajustáveis. Próximo, os pesquisadores planejam ajustar o chip para executar todos os esquemas de criptografia baseados em rede listados na segunda fase do NIST.

Esta história foi republicada por cortesia do MIT News (web.mit.edu/newsoffice/), um site popular que cobre notícias sobre pesquisas do MIT, inovação e ensino.