Um novo design de chip fotônico reduz drasticamente a energia necessária para computar com luz, com simulações sugerindo que ele poderia operar redes neurais ópticas 10 milhões de vezes mais eficientemente do que suas contrapartes elétricas. Crédito:MIT News

Os pesquisadores do MIT desenvolveram um novo chip "fotônico" que usa luz em vez de eletricidade - e consome relativamente pouca energia no processo. O chip poderia ser usado para processar redes neurais massivas milhões de vezes mais eficientemente do que os computadores clássicos de hoje.

Redes neurais são modelos de aprendizado de máquina amplamente usados para tarefas como identificação de objetos robóticos, processamento de linguagem natural, Desenvolvimento de drogas, imagens médicas, e movimentando carros sem motorista. Novas redes neurais ópticas, que usam fenômenos ópticos para acelerar a computação, podem funcionar com muito mais rapidez e eficiência do que suas contrapartes elétricas.

Mas, à medida que as redes neurais tradicionais e ópticas ficam mais complexas, eles consomem toneladas de energia. Para resolver esse problema, pesquisadores e grandes empresas de tecnologia, incluindo o Google, IBM, e Tesla - desenvolveram "aceleradores de IA, "chips especializados que melhoram a velocidade e a eficiência do treinamento e do teste de redes neurais.

Para chips elétricos, incluindo a maioria dos aceleradores de IA, existe um limite mínimo teórico para o consumo de energia. Recentemente, Os pesquisadores do MIT começaram a desenvolver aceleradores fotônicos para redes neurais ópticas. Esses chips desempenham ordens de magnitude com mais eficiência, mas eles contam com alguns componentes ópticos volumosos que limitam seu uso a redes neurais relativamente pequenas.

Em um artigo publicado em Revisão Física X , Os pesquisadores do MIT descrevem um novo acelerador fotônico que usa componentes ópticos mais compactos e técnicas de processamento de sinal óptico, para reduzir drasticamente o consumo de energia e a área de chip. Isso permite que o chip seja dimensionado para redes neurais várias ordens de magnitude maior do que suas contrapartes.

O treinamento simulado de redes neurais no conjunto de dados de classificação de imagem MNIST sugere que o acelerador pode teoricamente processar redes neurais mais de 10 milhões de vezes abaixo do limite de consumo de energia de aceleradores elétricos tradicionais e cerca de 1, 000 vezes abaixo do limite dos aceleradores fotônicos. Os pesquisadores agora estão trabalhando em um protótipo de chip para provar experimentalmente os resultados.

"As pessoas estão procurando por tecnologia que possa computar além dos limites fundamentais de consumo de energia, "diz Ryan Hamerly, pós-doutorado no Laboratório de Pesquisa em Eletrônica. "Os aceleradores fotônicos são promissores ... mas nossa motivação é construir um [acelerador fotônico] que pode escalar até grandes redes neurais."

As aplicações práticas para essas tecnologias incluem a redução do consumo de energia em data centers. "Há uma demanda crescente por data centers para executar grandes redes neurais, e está se tornando cada vez mais intratável computacionalmente conforme a demanda cresce, "diz o co-autor Alexander Sludds, Pós-graduando no Laboratório de Pesquisa em Eletrônica. O objetivo é "atender à demanda computacional com hardware de rede neural ... para resolver o gargalo de consumo de energia e latência."

Juntando-se a Sludds e Hamerly no papel estão:co-autora Liane Bernstein, um aluno de pós-graduação RLE; Marin Soljacic, um professor de física do MIT; e Dirk Englund, um professor associado do MIT de engenharia elétrica e ciência da computação, um pesquisador no RLE, e chefe do Laboratório de Fotônica Quântica.

Design compacto

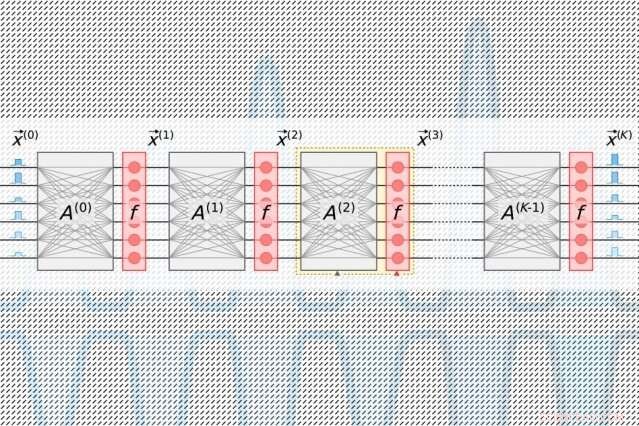

As redes neurais processam dados através de muitas camadas computacionais contendo nós interconectados, chamados de "neurônios, "para encontrar padrões nos dados. Os neurônios recebem entrada de seus vizinhos a montante e calculam um sinal de saída que é enviado aos neurônios mais a jusante. Cada entrada também recebe um" peso, "um valor baseado em sua importância relativa para todas as outras entradas. À medida que os dados se propagam" mais profundamente "através das camadas, a rede aprende progressivamente informações mais complexas. No fim, uma camada de saída gera uma previsão com base nos cálculos em todas as camadas.

Todos os aceleradores de IA visam reduzir a energia necessária para processar e mover dados durante uma etapa específica de álgebra linear em redes neurais, chamada de "multiplicação de matrizes". Lá, neurônios e pesos são codificados em tabelas separadas de linhas e colunas e então combinados para calcular os resultados.

Em aceleradores fotônicos tradicionais, lasers pulsados codificados com informações sobre cada neurônio em um fluxo de camada em guias de onda e através de divisores de feixe. Os sinais ópticos resultantes são alimentados em uma grade de componentes ópticos quadrados, chamados de "interferômetros Mach-Zehnder, "que são programados para realizar a multiplicação da matriz. Os interferômetros, que são codificados com informações sobre cada peso, use técnicas de interferência de sinal que processam os sinais ópticos e os valores de peso para calcular uma saída para cada neurônio. Mas há um problema de escala:para cada neurônio deve haver um guia de ondas e, para cada peso, deve haver um interferômetro. Porque o número de pesos quadrados com o número de neurônios, esses interferômetros ocupam muito espaço.

"Você percebe rapidamente que o número de neurônios de entrada nunca pode ser maior do que 100 ou mais, porque você não pode encaixar tantos componentes no chip, "Hamerly diz." Se o seu acelerador fotônico não pode processar mais de 100 neurônios por camada, então, fica difícil implementar grandes redes neurais nessa arquitetura. "

O chip dos pesquisadores depende de uma forma mais compacta, esquema "optoeletrônico" de eficiência energética que codifica dados com sinais ópticos, mas usa "detecção homódina balanceada" para multiplicação de matrizes. É uma técnica que produz um sinal elétrico mensurável após calcular o produto das amplitudes (alturas de onda) de dois sinais ópticos.

Pulsos de luz codificados com informações sobre os neurônios de entrada e saída de cada camada da rede neural - que são necessários para treinar a rede - fluem por um único canal. Pulsos separados codificados com informações de linhas inteiras de pesos na tabela de multiplicação da matriz fluem por canais separados. Os sinais ópticos que transportam o neurônio e os dados de peso se espalham para a grade de fotodetectores homodinos. Os fotodetectores usam a amplitude dos sinais para calcular um valor de saída para cada neurônio. Cada detector alimenta um sinal elétrico de saída para cada neurônio em um modulador, que converte o sinal de volta em um pulso de luz. Esse sinal óptico se torna a entrada para a próxima camada, e assim por diante.

O projeto requer apenas um canal por neurônio de entrada e saída, e apenas tantos fotodetectores homódinos quantos forem os neurônios, não pesos. Porque sempre há muito menos neurônios do que pesos, isso economiza espaço significativo, portanto, o chip pode ser dimensionado para redes neurais com mais de um milhão de neurônios por camada.

Encontrando o ponto ideal

Com aceleradores fotônicos, há um ruído inevitável no sinal. Quanto mais luz é alimentada no chip, quanto menos ruído e maior a precisão, mas isso se torna bastante ineficiente. Menos luz de entrada aumenta a eficiência, mas afeta negativamente o desempenho da rede neural. Mas há um "ponto ideal, "Bernstein diz, que usa potência óptica mínima, mantendo a precisão.

Esse ponto ideal para aceleradores de IA é medido em quantos joules são necessários para realizar uma única operação de multiplicação de dois números - como durante a multiplicação da matriz. Agora mesmo, aceleradores tradicionais são medidos em picojoules, ou um trilionésimo de joule. Aceleradores fotônicos medem em attojoules, que é um milhão de vezes mais eficiente.

Em suas simulações, os pesquisadores descobriram que seu acelerador fotônico poderia operar com eficiência sub-attojoule. "Há alguma potência óptica mínima que você pode enviar, antes de perder a precisão. O limite fundamental do nosso chip é muito menor do que os aceleradores tradicionais ... e menor do que outros aceleradores fotônicos, "Bernstein diz.

Esta história foi republicada por cortesia do MIT News (web.mit.edu/newsoffice/), um site popular que cobre notícias sobre pesquisas do MIT, inovação e ensino.