Os pesquisadores do NIST foram pioneiros em um processo que simplifica drasticamente a fabricação do tipo de recursos de microchip em nanoescala que podem em breve formar a base de um computador quântico, entre outras aplicações.

Em vez de bits de computador convencionais 1 ou 0 armazenados na forma de cargas elétricas, as informações quânticas são armazenadas e manipuladas na forma de bits quânticos (qubits), que pode ter vários valores simultaneamente. Um candidato qubit altamente promissor é um único átomo de elementos como o fósforo (P) enterrado em silício-28 ultra-puro.

Esses átomos podem ser colocados com precisão usando um microscópio de tunelamento de varredura (STM), um instrumento de laboratório robusto amplamente disponível para cientistas que podem não ter acesso a outras ferramentas complexas de nanofabricação.

Usar um STM para a fabricação de qubit requer fazer conexões elétricas aos qubits P e depósitos semelhantes a fios com menos de 1/100 da largura de um cabelo humano. Até agora, que geralmente só é possível usando diferentes, instrumentos complicados e caros, cujo custo pode facilmente ultrapassar US $ 10 milhões, e usando oneroso, procedimentos de alinhamento únicos para coordenar as diferentes etapas e localizar os qubits.

"Estamos pegando o que agora é um processo complexo e um tanto esotérico e simplificando-o para que seja muito mais fácil e eficiente de realizar, "disse o pesquisador do NIST, Josh Pomeroy, que com colegas relatam seu trabalho na Nature Scientific Reports. "Ele melhora a acessibilidade e a capacidade de fabricação em longo prazo por meio da padronização e está mais bem alinhado com os processos industriais estabelecidos."

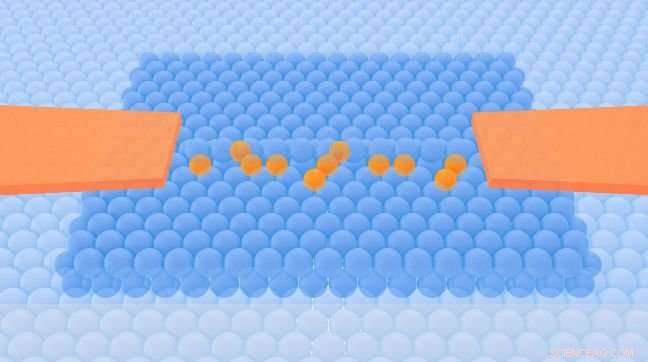

Os componentes críticos que formam os qubits são átomos de P - que agem como um metal no silício - cujas posições são determinadas pelo STM antes de serem selados com uma camada protetora de silício cristalino. No método convencional, os pesquisadores normalmente fazem contatos elétricos com os depósitos enterrados depois que o chip é selado, usando um método chamado litografia por feixe de elétrons (um processo difícil e caro) para cortar canais na camada externa e definir fios de metal. Mas primeiro eles devem localizar precisamente os depósitos enterrados, um processo lento e meticuloso.

"O problema é que agora você tem, em algum lugar neste chip, um recurso na escala de um micrômetro [um milionésimo de metro] nos 40 do chip, 000, Área de superfície de 000 micrômetros quadrados [4 mm x 10 mm], "Pomeroy disse." E, essencialmente, tudo isso é silício. É como tentar encontrar uma agulha específica em um enorme palheiro de agulhas. Primeiro, você tem que localizar o depósito por varredura de 'força bruta', em seguida, registre sua posição em referência a algum outro recurso do chip, e, finalmente, desenhe um padrão personalizado que conecte os depósitos. "

O método pioneiro do NIST cria padrões de fio de P em wafers de silício inteiros no início, usando um método de "implante" padrão da indústria para colocar fios de interconexão muito antes de qualquer padronização de STM. Cada wafer é então cortado em centenas de chips usados para o trabalho de STM, melhorando substancialmente a eficiência. Com os depósitos de P em grande escala já instalados, o chip é carregado no STM, preparado, e sua superfície é coberta por uma camada uniforme de átomos de hidrogênio. As marcas de guia feitas durante a etapa do implante conduzem o STM ao local correto no chip.

"Quando trazemos pela primeira vez a ponta STM para a amostra, "Pomeroy disse, "estamos imediatamente no código postal correto. E, em seguida, usando os recursos de imagem do STM, podemos 'ver' diretamente o implantado, regiões eletricamente ativas. Então, quando você desenha o padrão, você sabe exatamente onde estão os fios e se conecta diretamente a eles. "

A ponta STM desenha caminhos entre o P implantado e outras características, removendo átomos de hidrogênio para fazer um modelo litográfico. Com o padrão estabelecido, a superfície é exposta à fosfina, um composto de fósforo-hidrogênio, e aquecido de modo que apenas P permaneça para trás no padrão, formando pontos quânticos e nanofios cujo tamanho pode variar de 100 nm até tão pequeno quanto um único átomo. Para preservar e medir o dispositivo, uma camada cristalina de Si é depositada sobre todo o sistema. Como o STM já conectou os nano-recursos aos fios implantados maiores, nenhuma informação adicional é necessária para completar o contato elétrico, o que é feito por uma etapa simples que adiciona metal a locais predefinidos.

Para desenvolver o novo método, Cientistas do NIST e colaboradores da Universidade de Maryland, College Park teve que resolver um problema de duas necessidades concorrentes. Vários fios tiveram que estar próximos para serem alcançados com o STM, mas não conectado eletricamente. Para descobrir um equilíbrio, eles precisavam entender e modelar o efeito do aquecimento nos depósitos implantados durante a fabricação do chip. Tipicamente, Substratos de Si são preparados para STM por aquecimento "flash" acima de 1200 ° C por aproximadamente um minuto, o que pode causar uma quantidade significativa de difusão do implante. A difusão pode fazer com que fios muito espaçados se fundam em um só.

"Quando propusemos o conceito pela primeira vez, "Pomeroy disse, "muitas pessoas tinham todos os tipos de ideias sobre por que não funcionaria - com as quais concordamos. Mas tentamos mesmo assim, e encontrou uma maneira de torná-lo bem-sucedido. Antes, era necessário muito equipamento altamente sofisticado e técnica árdua para fabricar chips desse tipo. Agora, um professor com um sistema STM e alguns alunos de pós-graduação podem entrar no jogo. Isso deve acelerar o ritmo de descoberta neste campo altamente promissor. "

Esta história foi republicada por cortesia do NIST. Leia a história original aqui.