Crédito:Gramse et al.

Ao fabricar circuitos integrados e diferentes tipos de dispositivos baseados em silício, os pesquisadores precisam posicionar nanoestruturas dopantes de maneiras específicas com altos níveis de precisão. Contudo, organizar essas estruturas em escala nanométrica pode ser desafiador, como seu tamanho pequeno torna difícil observá-los e examiná-los de perto. A adulteração incorreta deles pode ter efeitos prejudiciais, o que pode comprometer o funcionamento geral e a segurança de um dispositivo.

Com isso em mente, pesquisadores da Universidade Johannes Kepler (JKU), Keysight Technologies Labs, University College London (UCL), e a IBM Research iniciou recentemente o desenvolvimento de uma técnica de imagem em nanoescala que pode ser usada para observar nanoestruturas dopantes em dispositivos baseados em silício com alta precisão. O método que desenvolveram, apresentado em um artigo publicado em Nature Electronics , é o resultado de vários anos de pesquisa, na sequência de um projeto conjunto Marie Curie-EU que teve início em 2016.

"No JKU e no Keysight Technologies Labs, eu estava trabalhando no desenvolvimento de novas técnicas de caracterização em nanoescala que podem observar as propriedades elétricas em nanoescala de pequenos recursos abaixo da superfície de um material, "Georg Gramse, um dos pesquisadores que realizou o estudo, disse a Phys.org. "A grande questão para nós era:quão pequeno podemos ir ou quão fundo podemos olhar e ainda ver dopantes ou outros recursos condutores? A questão de nossos colegas do London Centre for Nanotechnology (LCN) e da IBM que se juntaram à equipe um pouco depois foi exatamente o oposto:Onde estão nossas estruturas dopantes? Elas estão onde deveriam estar, e eles estão ativados e conduzindo? "

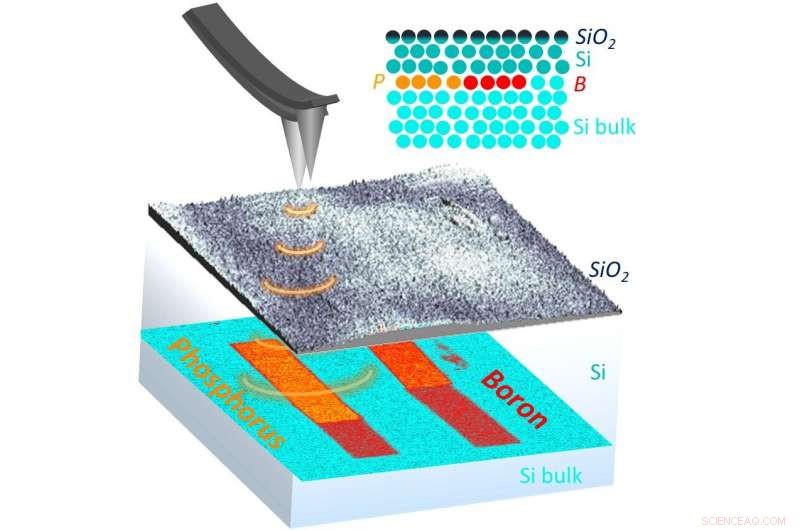

Os pesquisadores do JKU e do Keysight Technologies Labs desenvolveram métodos que podem criar nano-padrões de camadas dopantes atomicamente finas do tipo n (fósforo) e do tipo p (boro) em silício, bem como suas junções p-n resultantes. Isso foi feito em estreita colaboração com especialistas em nanotecnologia da UCL e da IBM.

Até aqui, os pesquisadores não encontraram uma única técnica capaz de medir a localização 3-D e as características elétricas de nanoestruturas dopantes em dispositivos de silício, ao mesmo tempo em que coletam informações sobre a dinâmica de carga de portadores e cargas aprisionadas em seus arredores. Para alcançar isto, Gramse e seus colegas usaram uma técnica chamada microscopia de força eletrostática de banda larga. Este método pode coletar imagens com uma resolução mais alta do que aquelas coletadas usando técnicas de imagem padrão e também não é destrutivo, o que significa que não danifica um dispositivo durante a coleta de medições.

"Nossa técnica resolve lateralmente com 10 nm, mesmo se um recurso estiver enterrado 15 nm abaixo da superfície, e detecta a assinatura de capacitação de cargas subterrâneas em frequências entre 1kHz e 10GHz, "Gramse disse." Uma de suas desvantagens, compartilhada por outras técnicas em nanoescala, é que, para dar essa alta resolução, ele precisa de uma superfície limpa e relativamente plana. "

Gramse e seus colegas foram os primeiros a desenvolver uma técnica que pode extrair com sucesso informações quantitativas sobre a profundidade e o perfil dopante de nanoestruturas em dispositivos de silício. O método que eles usaram também permitiu coletar informações sobre a dinâmica dos portadores e cargas aprisionadas em torno dessas estruturas. Essas informações podem ajudar a determinar se há alguma armadilha no dispositivo de silício, o que pode obstruir o movimento de dopantes em seu interior.

"Vejo muitos campos de aplicação possíveis para nossa técnica, "Gramse disse." Vamos agora continuar investigando imagens de dispositivos de dopagem funcionais. Observar a dinâmica dos processos elétricos em nanoescala também é de grande interesse em materiais eletroquímicos e de energia, portanto, este será outro tópico para enfocar em nosso trabalho futuro. "

© 2020 Science X Network